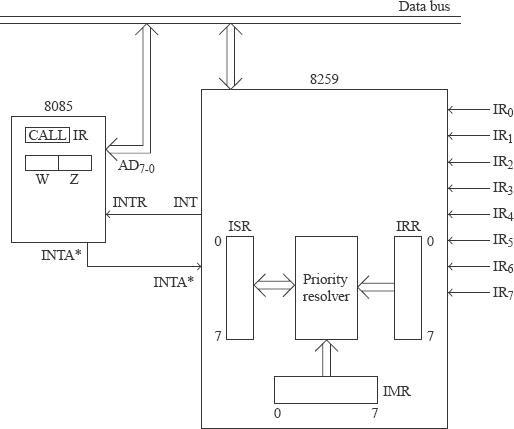

8259 的架构

8259 微处理器采用独特的设计。它可以通过一些中断条件,即电平或中断电平(也称为边缘触发中断电平)进行编程。对各个中断位进行屏蔽。随着 8259 的增加,最多可获得 64 个中断引脚。8259 包含 3 个寄存器以及一个优先级解析器 (PR)。它们如下所示 −

中断请求寄存器 (IIR) − 存储请求中断的位。

中断服务寄存器 (ISR) − 存储当前中断级别。

中断屏蔽寄存器 (IMR) − 存储要屏蔽的中断级别。

优先级解析器 (PR) − 通过检查所有三个寄存器并设置 ISR 中具有最高优先级的中断级别来设置中断的优先级。

SP/EN(低电平激活引脚) − 当其值为 1 时,它在主模式下工作,当其值为 0 时,它在从模式下工作。

级联缓冲区 − 用于级联更多可编程中断控制器。

图 − 8259 与 8085 处理器接口

广告

数据结构

数据结构 网络

网络 关系型数据库管理系统

关系型数据库管理系统 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 语言编程

C 语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL JavaScript

JavaScript PHP

PHP