计算机体系结构中的总线传输是什么?

总线传输是利用公共总线系统发送数据的最有效方法。它使用多个寄存器中的公共总线寄存器构建。总线机制包括一组线路。这些线路是每个一位的寄存器,一次只共享一条信息。数据传输由控制信号包含。

总线传输可以使用以下两种方法:

- 使用多路复用器

- 使用三态总线缓冲器

使用多路复用器

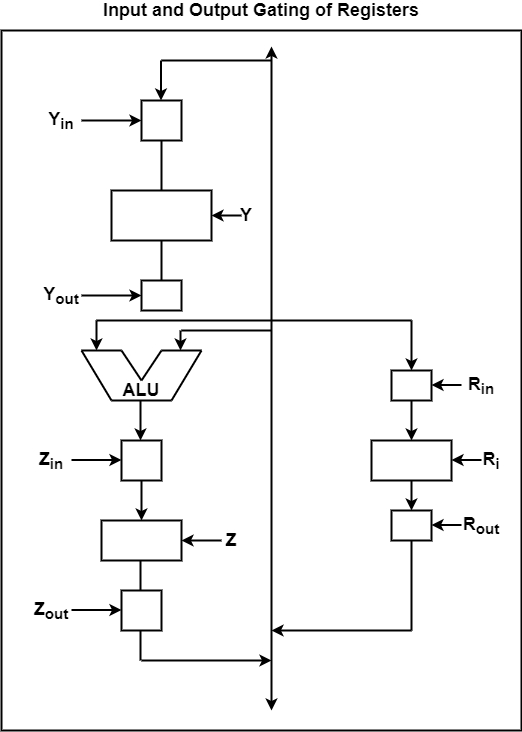

可以使用多路复用器生成公共总线。它有助于选择源寄存器将二进制数据放置在总线上。总线寄存器具有由控制信号控制的输入和输出门控。该图演示了寄存器的输入和输出门控。

- Ri 是寄存器,Rin 和 Rout 是 Ri 的输入和输出门控信号。

- Z 是寄存器,Zin 和 Zout 是寄存器 Z 的输入和输出门控信号。

- Y 是寄存器,Yin 和 Yout 是 Y 的输入和输出信号。

该图显示了输入和输出门控。开关由控制信号控制。Rin 和 Rout 是寄存器 Ri 的输入和输出门控。当信号打开时,Ri 设置为 1,当信号关闭时,Ri 设置为 0。

当输入门控 Rin 设置为 1 时,数据将加载到寄存器总线 Ri 中,该总线可在公共总线上访问。当 Rout 设置为 1 时,寄存器 Ri 的内容将放置在数据总线上。它被称为输入使能和输出使能信号。处理器内部发生的函数与时钟脉冲同步。

三态缓冲器

三态缓冲器可以生成公共总线。缓冲器是内存的一个区域,它添加到其他设备之间以阻止多个交互并连接支持。它建立在三种状态上,1、0 和开路。这三种状态定义如下:

- 逻辑 0 和 1 是与传统门中相同的两个信号。

- 高阻抗状态定义它不包含逻辑意义,并且输出已分离。

- 这些三态门可以实现任何传统的逻辑 AND 或 NAND、OR 或 NOR。

该图演示了逻辑符号和相关的真值表。

如图所示:

- 当允许输出并且控制输入类似于 1 时。逻辑门充当缓冲器,输出类似于输入。

- 当提供的输入为 0 时,门进入高阻抗状态 Z,并且输出被禁用。

- 三态缓冲器中的阻抗将所有输出与电缆连接以产生公共总线线路,并且不会威胁加载效果。

- 真值表显示,当给出某些输入并且门被禁用时,它显示为高阻抗。

- 当门被启用并给出一些输入时,输出结果不会处于禁用模式。

- 当门被启用且输入为 1 时,输出类似于 1。

广告

数据结构

数据结构 网络

网络 关系型数据库管理系统

关系型数据库管理系统 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP