计算机体系结构中的指令流水线是什么?

指令流水线从内存中读取连续的指令,而在其他段中,先前的指令正在执行。流水线处理出现在数据流和指令流中。这导致指令的获取和执行重叠,从而执行同时操作。

这种设计可能还与另一个事件相关,即指令可能会生成一个分支,跳出指令序列。在这种方法中,流水线被清空,并且分支指令之后从内存中读取的所有指令都应被丢弃。

计算机可以构建为支持一个两段单元,包括一个指令获取单元和一个指令执行单元。使用先进先出 (FIFO) 缓冲区实现指令获取段。

这是一种单元形成队列而不是堆栈的方法。当执行单元未访问内存时,控制器会递增程序计数器并帮助其地址值从内存中读取连续指令。

指令被插入到 FIFO 缓冲区中,以便执行以 FIFO 的方式出现。因此,指令流可以驻留在队列中,等待执行段进行解码和阶段化。

因此,指令流排队结构提供了一种有效的方法来减少读取指令的内存平均访问时间。只要 FIFO 缓冲区中有可用空间,控制单元就会启动下一个指令获取步骤。

缓冲区充当队列,执行单元从中获取指令以进行处理。

具有复杂指令的设备除了获取和执行之外,还需要其他步骤才能彻底处理指令。在这种方法中,设备需要按照以下步骤序列处理每条指令。

- 它可以从内存中获取指令。

- 它可以解码指令。

- 它可以计算有效地址。

- 它可以从内存中获取操作数。

- 它可以执行指令。

- 它可以将结果保存到合适的位置。

多个段可能需要不同的时间来处理传入的数据。这可能会阻止指令流水线以其最大速度运行。对于某些操作,会跳过一些段。

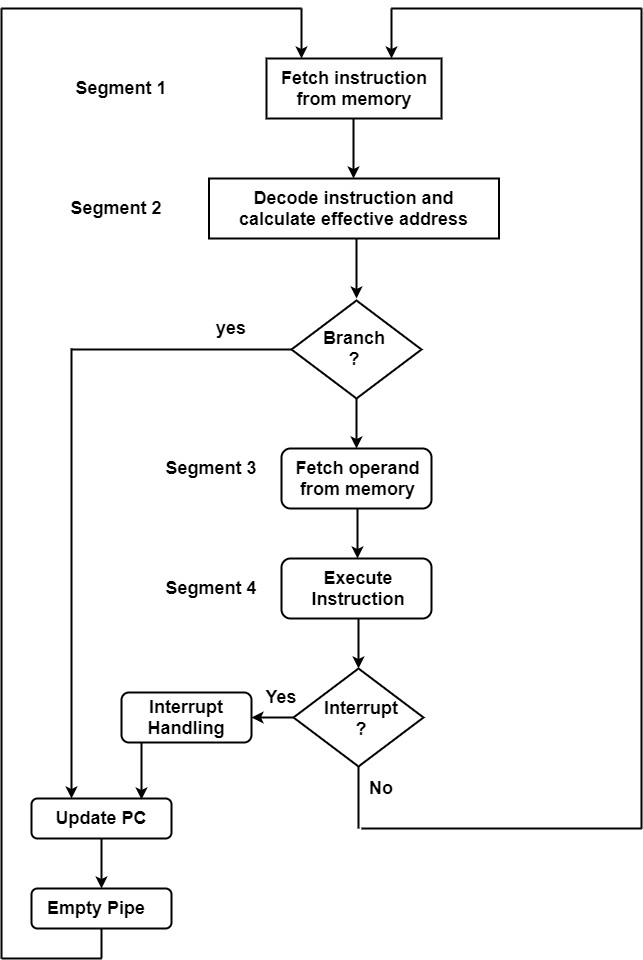

该图显示了指令流水线的示例。

段 1

可以使用先进先出 (FIFO) 缓冲区执行指令获取段。

段 2

从内存中获取的指令在第二个段中进行解码。有效地址在一个独立的算术电路中计算。

段 3

在第三个段中从内存中获取操作数。

段 4

指令最终在流水线组织的最后一个段中执行。

广告

数据结构

数据结构 网络

网络 关系数据库管理系统

关系数据库管理系统 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 编程

C 编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP