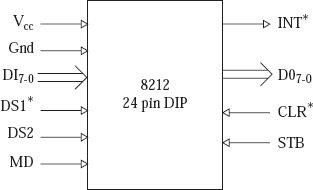

8212 非可编程8位I/O端口

输入输出端口分为两种:可编程输入输出端口和非可编程输入输出端口。由于可编程输入输出端口的功能可以通过软件改变,因此它们变得更受欢迎。我们不需要改变线路,而是改变I/O端口的硬件来改变其功能。Intel 8255是一个基于端口的流行输入输出芯片。而对于非可编程I/O端口,需要改变线路或硬件来改变其完整功能。我们稍后会看到,当8212作为输入端口而不是输出端口工作时,需要改变连接。这些非可编程的输入输出端口设计简单。

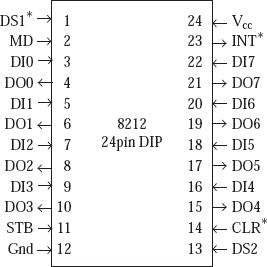

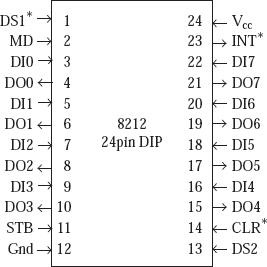

如今,我们发现8212作为双列直插式封装芯片,共有24个引脚。

它需要+5V的直流电源才能工作。8212中的8位锁存器接收来自DI7到DI0的八个数据输入上的信息。帮助信息锁存的条件取决于MD引脚的逻辑状态。锁存器中的信息通过D7-D0数据输出引脚输出。信息锁存的条件取决于MD引脚。

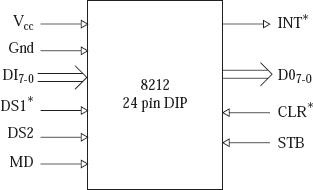

如今,我们发现8212作为双列直插式封装芯片,共有24个引脚。

它需要+5V的直流电源才能工作。8212中的8位锁存器接收来自DI7到DI0的八个数据输入上的信息。帮助信息锁存的条件取决于MD引脚的逻辑状态。锁存器中的信息通过D7-D0数据输出引脚输出。信息锁存的条件取决于MD引脚。

8212依赖于边沿触发的D型触发器。我们称之为服务请求触发器。它负责在INT*引脚上生成中断请求。INT*是一个低电平有效的输出引脚,在中断驱动的数据传输方案中很有用。负责激活INT*信号的内部架构如下所示

当DS1*为0且DS2为1时,内部芯片选择信号被激活。

当STB由高电平转为低电平时,内部信号SQ为0。

图:8212中触发器锁存的连接细节

从图中可以得出以下结论:当MD为1时,CS充当锁存器的时钟;当MD为0时,STB充当锁存器的时钟。当时钟处于高电平时,锁存器的输出Q跟随相应的DI输入。当时钟由高电平转为低电平时,数据锁存开始起作用。当EN信号被激活时,输出Q处的数据通过相应的DO引脚输出。当CS等于1或MD等于1时,EN信号被激活。

简要概述一下引脚:

| Vcc | 始终连接到+5V的直流电源。 |

| Gnd | 连接到地。 |

| MD | 模式输入引脚,确定锁存器的时钟源。如果MD为0,则STB充当锁存器的时钟输入;如果MD为1,则CS充当时钟输入。 |

| STB | 脉冲输入。 |

| DS1*, DS2 | 器件选择引脚。 |

| DI7-0 | 八个数据输入,从D7到D0。 |

| DO7-0 | 数据输出。 |

| INT* | 中断输出引脚,用于中断微处理器。 |

| CLR* | 异步清零输入,低电平有效。 |

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP