计算机体系结构中BCD加法器的框图?

BCD加法器指的是一个4位二进制加法器,可以对两个4位BCD格式的字进行加法运算。加法的结果是一个BCD格式的4位输出字。它可以描述被加数和加数的十进制和,以及在该和超过9的十进制值时产生的进位。因此,BCD加法器可以执行十进制加法。

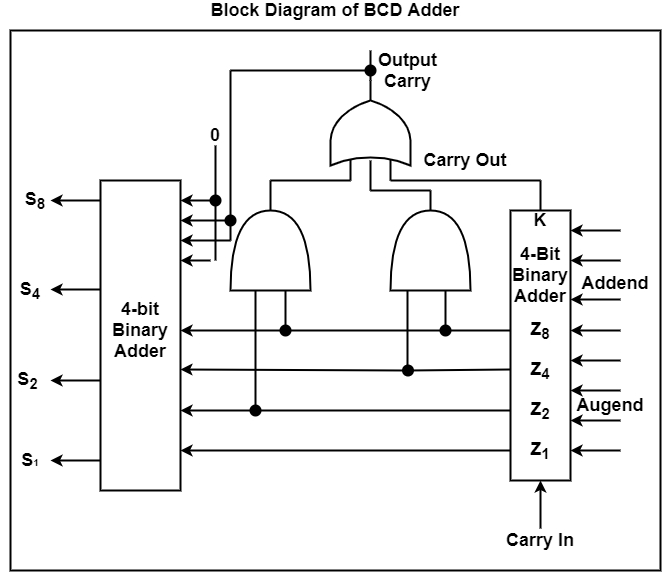

BCD加法器是一个电路,它并行地对两个BCD数字进行加法运算,并生成一个也是BCD格式的和数位。BCD加法器在其内部结构中应该包含校正逻辑。为了将0110添加到二进制和中,我们使用第二个4位二进制加法器,如图所示。

两个十进制数字以及输入进位首先在顶部的4位二进制加法器中相加,以产生二进制和。当输出进位为0时,不会将任何内容插入二进制和中。当它为1时,二进制0110通过底部的4位二进制加法器插入二进制和中。从最低位二进制加法器产生的输出进位可以被丢弃,因为它已经提供了在输出进位端子中可以访问的数据。

一个对n个十进制数字进行加法运算的十进制并行加法器需要n个BCD加法器阶段,其中一个阶段的输出进位连接到下一个更高阶阶段的输入进位。为了实现更短的传播延迟,BCD加法器包括必要的超前进位电路。此外,校正加法器电路不需要全部四个全加器,并且该电路可以进行优化。

广告

数据结构

数据结构 网络

网络 关系数据库管理系统(RDBMS)

关系数据库管理系统(RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP