计算机体系结构中的二进制加法器-减法器是什么?

二进制数的减法可以通过创建被加数位的2的补码并将其插入到加数位来有效地完成。2的补码可以通过取1的补码并在最低有效位对插入1来获得。

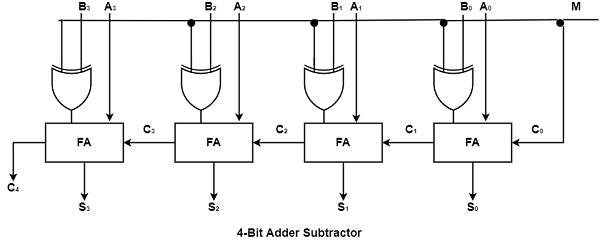

1的补码可以使用反相器执行,并且可以通过输入进位将1插入到和中。加法和减法运算可以通过包含每个全加器的异或门合并到一个联合电路中。图中演示了一个4位加法器-减法器电路。

模式输入M控制操作。当M=0时,电路为加法器;当M=1时,电路变为减法器。每个异或门接收输入M和B的一个输入。当M=0时,我们有B ⊕ 0 = B。

全加器接收B的值,输入进位为O,电路执行A加B。当M=1时,我们有B ⊕ 1 = B' 和C0 = 1。B输入全部取反,并且通过输入进位插入1。

电路执行A加上B的2的补码。对于无符号数,如果A \geq B,则得到A - B;如果A < B,则得到(B - A)的2的补码。对于有符号数,结果为A - B,前提是没有溢出。

广告

数据结构

数据结构 网络

网络 关系数据库管理系统

关系数据库管理系统 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 编程

C 编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP