8085微处理器内存速度要求

在机器周期状态T2结束时,8085处理器会检测Ready输入引脚。如果为逻辑0,则8085处理器进入Twait 状态,否则进入T3状态。Ready输入永久固定为逻辑1。系统中的内存芯片和输入/输出端口与8085具有相同的速度。否则,外部电路应生成适当数量的等待状态。实际上,在ALS套件中,Ready引脚应固定为逻辑1。

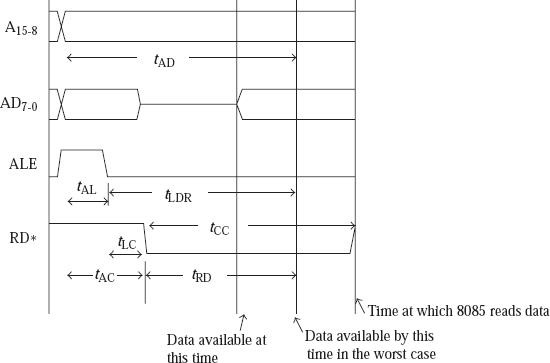

例如,我们检查一下,如果使用27128A-20 16K×8 EPROM芯片,并且在不使用任何等待状态的情况下与工作在320 nS时钟周期的8085处理器一起使用。因此,对于接口内存芯片,最重要的时序参数是tcc、tCE和tOE。

对于27128A-20芯片,其特性如下。

tAcc最大值为200 nS

tCE最大值为200 nS

tOE最大值为75 nS

在以下假设下,在接收稳定地址后,数据输出需要最多200 nS的时间。

内存芯片应至少在数据通过它输出前200 nS (tCE)被选中。

在输出数据之前,内存芯片的输出使能线应至少激活75 nS (tOE)。

广告

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP