8085微处理器架构

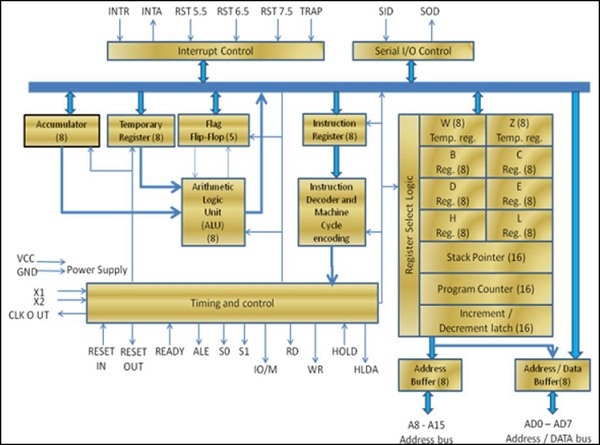

下图所示的8085微处理器架构由多个单元组成,每个单元都有其各自的功能。

图:8085微处理器架构

这些单元列在下面:

累加器

在Intel 8085微处理器中,累加器是一个8位寄存器,用于存储8位数据并对其执行算术和逻辑运算。最终结果存储在累加器中。它也称为A寄存器。

算术逻辑单元 (ALU)

它主要执行8位算术运算,例如+、-、*、/,以及执行逻辑运算,例如AND、OR、NOT等。ALU从累加器和临时寄存器获取输入,在其上执行这些运算。处理必要的运算后,结果将存储回累加器。

定时和控制单元

该单元负责生成定时信号和控制信号,并控制Intel 8085微处理器的内部和外部活动。定时和控制单元非常重要,因为它同步寄存器和数据通过各个寄存器和其他单元的流程。它包括一个振荡器和控制器排序器,后者发送内部和外部数据及其他单元控制所需的控制信号。

以下是定时和控制信号:

- 控制信号 - READY,RD',WR',ALE

- 状态信号 - S0,S1,IO/M'

- DMA信号 - HOLD,HLDA

- 复位信号 - RESET IN,RESET OUT

通用寄存器

8085微处理器中有六个通用寄存器B、C、D、E、H和L。每个寄存器可以保存8位数据。它们可以成对工作,例如BC、DE和HL,以存储16位数据,其中HL对用作内存指针。

程序计数器

程序计数器是一个16位寄存器,用于存储要执行的下一条指令的内存地址位置。每当执行一条指令时,微处理器都会递增程序计数器,以便程序计数器指向将要执行的下一条指令的内存地址。

堆栈指针

堆栈指针也是一个16位寄存器。它用作内存指针。从堆栈中检索数据时(称为弹出操作),堆栈指针会递增;当数据加载到堆栈中时(称为压栈操作),堆栈指针会递减。

增量/减量寄存器

16位增量和减量寄存器用于将PC值和SP值分别加1或减1。可以在任何寄存器或内存位置上执行增量或减量操作。

地址和地址数据缓冲区

程序计数器和堆栈指针的内容加载到地址数据缓冲区和地址缓冲区中。这些缓冲区在用作数据时是双向的。CPU可以与内存和I/O芯片交换所需的数据,因为内存和I/O芯片连接到这些总线上。地址数据缓冲区连接到外部和内部总线,该总线包含8位。

临时寄存器

临时寄存器是一个8位寄存器,它保存算术和逻辑运算的临时数据。此寄存器只能由微处理器访问,程序员完全无法访问。

状态或标志寄存器

该寄存器实际上是一组触发器,用于给出不同操作结果的状态。当ALU执行操作时,结果将传输到内部数据总线,结果的状态将存储在触发器中。

这是一组5个触发器:

符号 (S) –如果MSB位=0,则数字为正,否则为负。

零 (Z) –如果ALU中执行的操作导致整个8位的值为0,则设置零标志,否则复位。

辅助进位 (AC) –如果ALU中执行的操作从低四位(D0到D3)生成向高四位(D4到D7)的进位,则设置AC标志,否则复位。

奇偶校验 (P) –如果结果包含偶数个1,则设置此标志;如果包含奇数个1,则复位此标志。

进位 (C) –如果ALU中执行的操作从D7生成到下一级的进位,则设置CY标志,否则复位。

中断控制

当微处理器正在执行主程序并且发生中断时,微处理器会将控制从主程序转移到处理传入的请求。请求完成后,控制将返回主程序。

8085中存在的中断信号是:

- INTR

- RST 7.5

- RST 6.5

- RST 5.5

- TRAP

串行输入/输出控制

它使用以下两条指令控制串行数据通信:SID(串行输入数据)和SOD(串行输出数据)。

指令寄存器和译码器

指令寄存器也是8位寄存器。指令寄存器专门用于存储从内存中获取的指令,例如添加两个数据、移动数据、复制数据等。

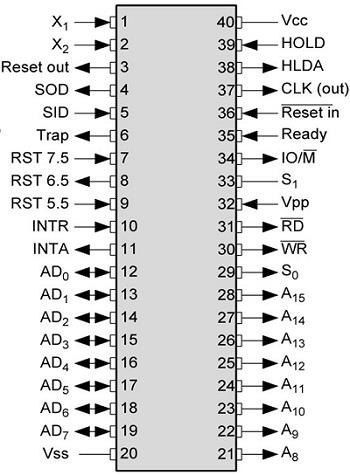

图:8085引脚图

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP