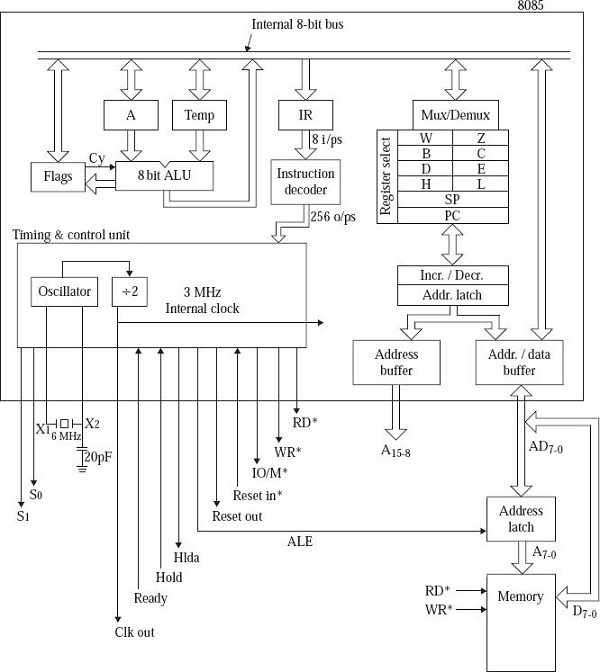

8085微处理器中的多路复用器/多路分解器

让我们考虑要执行的指令为“MOV A, C”。在这种情况下,必须将寄存器C中的8位值移动到累加器寄存器。给定的寄存器组,即B、C、D、E、H和L,必须通过多路复用器(多输入单输出)或多路分解器(多路复用器的反向)连接到内部总线。负责执行工作的寄存器选择特定的单元,并将相应的代码发送到多路复用器,以便寄存器C的内容通过内部总线发送到多路复用器。此后,累加器接收来自内部总线的数据。

让我们考虑给定指令“MOV D, A”的整个执行过程。在这种情况下,累加器的位值被移动到寄存器D。8位值被发送到累加器。寄存器B、C、D、E、H和L通过多路复用器/多路分解器连接到内部总线。给定的寄存器为多路分解器选择相应的代码,以便名为D的寄存器从内部总线接收所有内容到多路分解器。实际上,基本概念在于,在多路复用器中,许多输入合并形成一个输出。而多路分解器则适用反向过程。因此,在地址缓冲区中,我们发现执行的算术和逻辑序列操作涉及两个操作数,其中一个操作数由累加器提供,另一个操作数由临时寄存器提供。例如,在加法过程中,对B寄存器的指令,所有内容都被故意移动到临时寄存器,然后算术逻辑单元最终执行寄存器A和临时寄存器的加法。与W和Z类似

广告

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP