Parbegin / Parend 并发语句

在像 VHDL 这样的硬件描述语言中,"父"并发语句用于建立分层设计结构。它能够在一个组织内部创建和管理多个进程。

父并发语句的示例如下所示:

entity my_entity is

port (

clk: in std_logic;

reset: in std_logic;

data_in: in std_logic_vector(7 downto 0);

data_out: out std_logic_vector(7 downto 0)

);

end entity;

architecture behavioral of my_entity is

begin

-- Parent Concurrent Statement

parent_process: process(clk, reset)

begin

if reset = '1' then

-- Reset condition

data_out <_edge(clk) then

-- Child process 1

child1_process: process(data_in)

begin

-- some logic using data_in

data_out(0) <= data_in(0);

data_out(1) <= not data_in(1);

end process;

-- Child process 2

child2_process: process(data_in)

begin

-- some logic using data_in

data_out(2) <= data_in(2);

data_out(3) <= not data_in(3);

end process;

end if;

end process;

end architecture;

上面代码中存在一个名为 parent_process 的父进程。clk 和 reset 信号的变化启动了这个进程。

如果 reset 信号为高电平,则 data_out 信号被设置为零。当 reset 信号为低电平且 clk 出现上升沿时,会创建两个子进程,child1_process 和 child2_process。

这两个子进程中的每一个都在 data_in 信号发生变化时启动。它们使用 data_in 进行一些处理,并将值赋予 data_out 信号的特定位。

代码的逐步执行

为实体 my_entity 定义输入和输出端口。

根据架构行为定义,创建父进程并将其命名为 parent_process。

信号 clk 和 reset 导致父进程运行。

如果 reset 信号为高电平,则 data_out 信号被设置为零。

当 reset 信号为低电平且 clk 出现上升沿时,会创建两个子进程,child1_process 和 child2_process。

当 data_in 信号发生变化时,子进程使用 Data_in 执行一些逻辑。

data_out 信号的特定位。

直到发生另一个触发事件,父进程才会继续执行代码。

如何构造 Parend 并发语句?

Parbegin 是一种并发编程概念,它允许多个活动或进程同时运行。它将代码分成可以并发且独立运行的部分。Parbegin 的具体行为可能会根据所使用的平台或编程语言而有所不同。如果不小心使用 parbegin,可能会导致竞争条件和其他并发问题。

关键字 "generate" 后跟一个标签,并用关键字 "begin" 和 "end" 括起来,表示父并发语句。"If" 语句、"for" 循环和 "case" 语句是可以引入的其他并发语句。父并发语句的示例如下:

语法

gen_label: generate

for i in 0 to 3 generate

process_clk: process (clk)

begin

if rising_edge(clk) then

-- do something

end if;

end process process_clk;

end generate gen_label;

Parend 并发语句的优缺点

父并发语句提供了许多好处,但也有一些潜在的缺点,设计人员需要了解。使用父并发语句可能存在以下缺点:

缺点

时序问题

处理并发操作之间的时序依赖关系可能具有挑战性。例如,如果一个进程依赖于另一个进程的输出,则它可能需要等待另一个进程完成才能开始。这些时序约束可能会被引入,并且必须小心管理,以确保正确操作。

增加资源消耗

多个进程同时运行可能会消耗更多的内存和处理器时间。如果进程过多,则设计总体上可能会使用更多的资源。

有限的并行性

虽然父并发语句允许并行执行进程,但可用硬件资源可能会限制并行性的程度。如果硬件资源不足以支持所有并发进程,则某些并发进程可能需要序列化,这会降低并行处理的潜在优势。

调试包含多个并发进程的设计的问题

进程之间复杂的交互可能会使调试变得困难。如果问题涉及多个进程之间的交互,则可能难以查明根本原因。

总的来说,父并发语句有很多优点,但它们也可能增加一些额外的复杂性和挑战,需要仔细处理。在决定是否在给定设计中使用父并发语句时,设计人员应仔细权衡这样做的好处和坏处。

优点

父并发语句是一种用于数字电路设计的概念,它允许多个进程同时运行。父并发语句具有以下优点:

并行执行

父并发语句允许并行执行多个进程。能够同时执行多个任务可以提高设计的整体性能。

模块化设计

父并发语句允许采用模块化设计方法,其中不同的设计组件可以作为独立的进程执行。因此,它可以简化复杂和大型设计的管理,因为每个步骤都可以单独设计和测试。

更好的可读性

通过使用父并发语句,设计人员可以使代码更易于理解和维护。这是可能的,因为每个进程都可以作为一个单独的模块构建,具有清晰的接口以及明确定义的输入和输出。

更好的故障隔离

父并发语句可以帮助在设计中实现更好的故障隔离。一个进程中的故障不太可能影响同时运行的其他进程。

简化调试

在设计中使用父并发语句可以简化调试。可以独立地测试和调试每个进程,这可以加快识别和隔离问题。

总而言之,父并发语句是数字硬件设计人员的一项强大工具,它提供了许多优点,可以帮助提高设计的性能、可读性和可维护性。

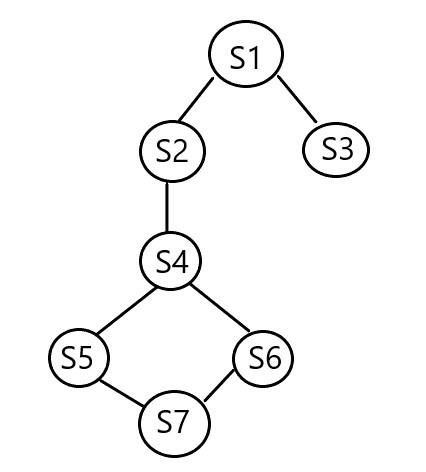

示例

VHDL 中的并发语句是指与设计中的其他语句同时执行的语句。带括号的并发语句是指使用括号将多个其他并发语句组合在一起的并发语句。以下是 VHDL 中带括号的并发语句的示例。

begin

S1;

parbegin

S3;

begin

S2;

parbegin

S4;

S5;

parend;

S6;

end;

parend;

S7;

end;

输出

在本例中,所有三个并发语句都将同时运行,因为它们包含在括号中。第一个语句中的进程在 clk 的上升沿时启动。第二个语句在 my_condition 为真时为 my_signal 赋值 "1",否则赋值 "0"。第三个语句将 my_input + 1 赋值给 My_output。

重要的是要记住,括号本身对并发语句的行为没有影响。它们仅仅是为了组织和可读性而将语句组合在一起。

结论

带括号的并发语句是在 VHDL 中使用的一种语句类型,它允许在一组括号内组合多个并发语句。这可以使设计更简单、更容易理解和维护。与所有 VHDL 结构一样,正确使用它并了解其限制和风险至关重要。并发语句允许在硬件设计中指定同时发生的进程,而无需使用顺序代码结构(如循环或 if-else 语句),使其成为硬件描述语言的重要组成部分。这可以提高设计性能和效率,因为它允许多个活动同时发生。它允许构建并行块,这些块可以帮助模块化复杂的行为,并通过共享变量或信号相互交互。

数据结构

数据结构 网络

网络 关系型数据库管理系统 (RDBMS)

关系型数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 语言编程

C 语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP