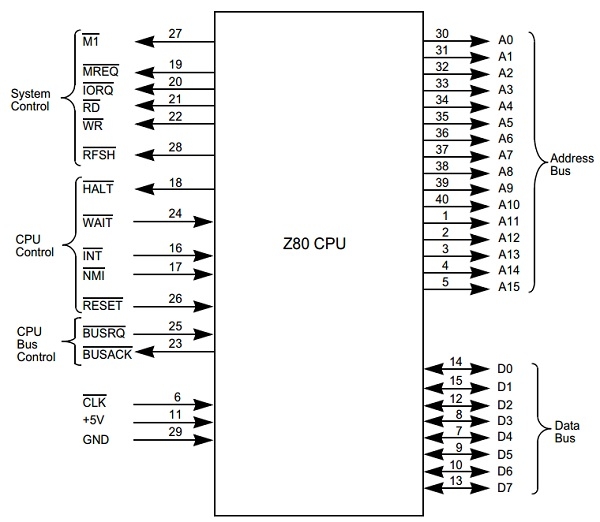

Z-80 引脚

Zilog Z-80 是一款 40 引脚 DIP 微处理器。在这里,我们将看到 Z-80 的实际引脚级图以及它的功能引脚图。

这是 Z-80 微处理器的实际引脚图。现在我们将看到它的功能引脚图。

现在让我们看看 Z-80 微处理器的引脚功能。

| 引脚 | 类型 | 功能 |

|---|---|---|

| A15 – A0 | 输出 | 16 位地址总线,提供内存地址(最多 64KB) |

| D7 – D0 | 输入/输出 | 8 位双向数据总线,用于在内存/IO 设备和 CPU 之间传输数据。 |

| BUSACK | 输出 | 它是总线应答引脚。它指示请求设备地址总线、数据总线、控制总线进入高阻抗状态。 |

| BUSREQ | 输入 | 总线请求引脚强制地址总线、数据总线和控制总线进入高阻抗状态。它总是在每个机器周期结束时被识别。 |

| HALT | 输出 | 停止状态指示 CPU 已执行停止指令并等待中断。 |

| INT | 输入 | 中断请求引脚用于由 IO 设备生成中断。执行每条指令后,CPU 检查中断请求。 |

| IORQ | 输出 | 输入输出请求引脚用于在需要与 IO 端口通信时返回低 (0) 信号。 |

| M1 | 输出 | 它指示机器周期 1。因此,当指令的第一个机器周期正在进行时,CPU 会激活此输出。 |

| MREQ | 输出 | 内存请求引脚用于在需要与内存块通信时返回低 (0) 信号。 |

| RD | 输出 | 它指示 CPU 想要从内存或 IO 设备读取数据。 |

| WR | 输出 | 它指示数据总线包含要存储在寻址的内存或 IO 位置中的数据。 |

| NMI | 输入 | 非屏蔽中断引脚是负边沿触发的。它的优先级高于INT。它不依赖于中断使能触发器的状态。它会自动强制 CPU 从地址 0066H 处重新启动。 |

| RESET | 输入 | 它重置当前的中断使能触发器,清除程序计数器 (PC) 以及 I 和 R 寄存器。地址和数据总线进入高阻抗状态。 |

| RFSH | 输出 | RFSH 和 MREQ 都可以用来指示地址总线的低 7 位可以作为动态内存的刷新地址。 |

| WAIT | 输入 | 此信号用于 CPU 和内存单元或 IO 设备之间的通信。在信号处于非活动状态之前,CPU 会连续进入等待状态。 |

| CLK | 输入 | 单相 MOS 电平时钟 |

广告

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 语言编程

C 语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP