计算机体系结构中的并行解码是什么?

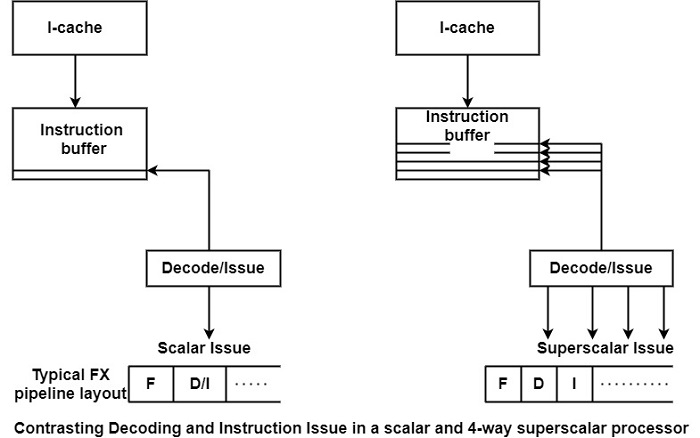

如图所示,标量处理器每个周期只能解码一条指令。此外,流水线处理器必须检查依赖关系,以确定是否可以发出该指令。相比之下,超标量处理器必须执行一项复杂得多的任务。

如图所示,它必须在一个时钟周期内解码多条指令,例如四条指令。它还需要从两个方面检查依赖关系:首先,要发出的指令是否依赖于当前正在执行的指令;其次,候选指令之间是否存在依赖关系。

由于超标量处理器比标量处理器拥有更多的执行单元 (EU),因此执行指令的数量远高于标量处理器的情况。这意味着在依赖性检查过程中必须执行更多比较。超标量处理器的解码-发出路径比标量处理器更关键,因为它关系到能否达到较高的时钟频率。

超标量处理器倾向于使用两个、甚至三个或更多个流水线周期来解码和发出指令。例如,PowerPC 601、PowerPC 604 和 UltraSparc 需要 2 个周期,而 α 21064 需要 3 个周期,PentiumPro 甚至需要 4.5 个周期。解决这个问题的一种方法是通过**预解码**。

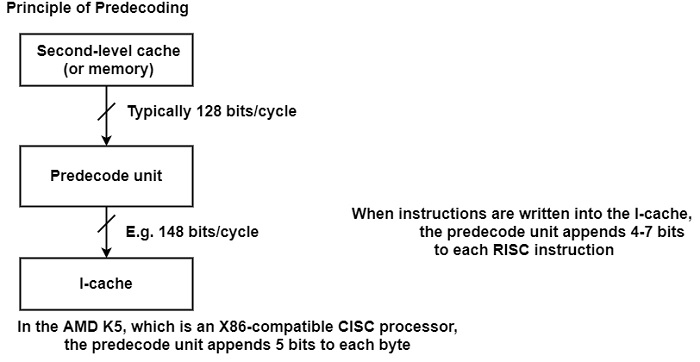

预解码将部分解码任务转移到片上指令缓存 (I-cache) 的加载阶段,如图所示。

在此,在加载 I-cache 的同时,一个称为预解码单元的专用单元执行部分解码,并将多个解码位连接到每条指令。例如,在 RISC 处理器的情况下,通常附加 4-7 位,这些位指示:

指令类别

执行所需资源的类型,以及

在某些处理器中,甚至包括分支目标地址已在预解码期间计算的事实,例如 Hal PM1 或 UltraSparc。

预解码单元的数量如表所示。

使用的预解码位数

| 首批批量发货的类型/年份 | 附加到每条指令的预解码位数 |

|---|---|

| PA 7200 (1995) | 5 |

| PA 8000 (1996) | 5 |

| PowerPC 620 (1996) | 7 |

| UltraSparc (1995) | 4 |

| HAL PM1 (1995) | 4 |

| AMD K5 (1995) | 5 |

| R10000 (1996) | 4 |

对于像 AMD K5 这样的 CISC 处理器,预解码可以确定指令的起始或结束位置、操作码和前缀的位置等等。这需要相当多的额外位。K5 为每个字节添加五个额外位。因此,在这种情况下,指令缓存需要超过 70% 的额外存储空间。

预解码用于缩短总周期时间或减少解码和指令发出所需的周期数。例如,PowerPC 620、R10000 和 Hal 的 PM1 的预解码只需要一个周期即可完成解码和发出。

数据结构

数据结构 网络

网络 关系型数据库管理系统 (RDBMS)

关系型数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP