指令发出率的设计空间是什么?

超标量处理器旨在为单个顺序程序产生每时钟周期超过一条指令的执行率。超标量处理器设计通常定义一组技术,使计算机的中央处理器 (CPU) 能够在实现单个顺序程序的同时获得每周期超过一条指令的吞吐量。

超标量指令发出概念最早于 1970 年提出 (Tjaden 和 Flynn,1970)。后来在 20 世纪 80 年代得到了更精确的重新表述 (Torng,1982,Acosta 等人,1986)。

超标量处理器的功能是超标量指令发出。更高的发出率会导致更高的处理器性能,但同时也会放大控制和数据依赖性对处理器性能的限制性影响。

在超标量处理器中,每个周期发出多条指令,控制依赖性比标量处理器出现的频率更高。频率的增加大致与处理器的发出率成正比。

至于数据依赖性,更高的发出率也会严重阻碍处理器性能。在此考虑一下,例如在流水线处理器中,通过使用并行优化编译器,大多数情况下可以避免由于依赖性造成的标量处理器发出阻塞。编译器使用单独的指令填充未使用的指令槽(称为气泡)。

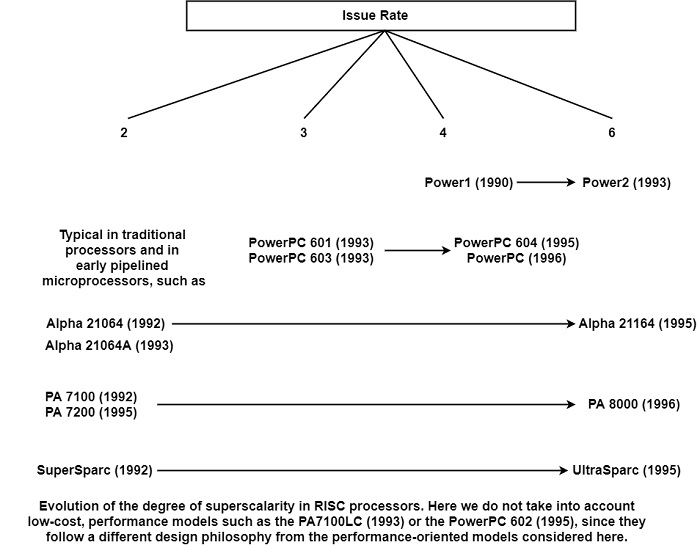

指令发出设计空间的第二个主要方面是发出率(超标量的程度)。此速率定义了超标量处理器在一个类似周期内可以发出的指令的最大数量。

超标量运算可以通过在每个周期发出两条、三条或更多条指令来执行。更高的发出率提供了更高的性能,但是,它的执行更加困难。

超标量 CISC 处理器通常被控制为每个周期仅发出两条或大约两条指令。相比之下,早期的超标量 RISC 处理器每个周期经常发出两条或三条指令。如所示,现代 RISC 处理器通常每个周期发出四条指令。

此图显示了五个特定 RISC 系列中发出率的演变。第一代 α 处理器 (α 21064 和 α 21064A) 和 HP 精确架构系列 (PA 7100、PA 7200) 的第一个超标量成员被控制为每个周期发出两条指令。

相比之下,PowerPC 系列 (PowerPC 601、PowerPC 603) 和 SuperSparc 的第一个成员能够每个周期发出三条指令,而 Power1 可以发出四条指令。

Power 2 在执行顺序路径时每个周期发出六条指令。但是,在猜测分支后,在开始执行目标路径时,处理器仅发出四条指令。因此,Power2 现在是发出率的领导者。

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP