8255 并行接口(PPI)描述

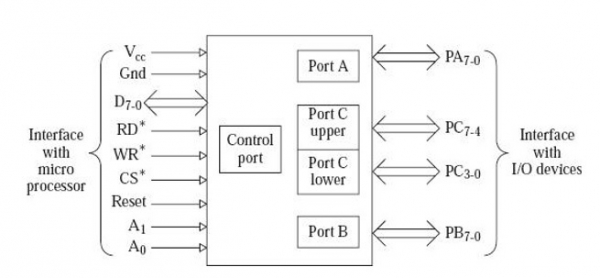

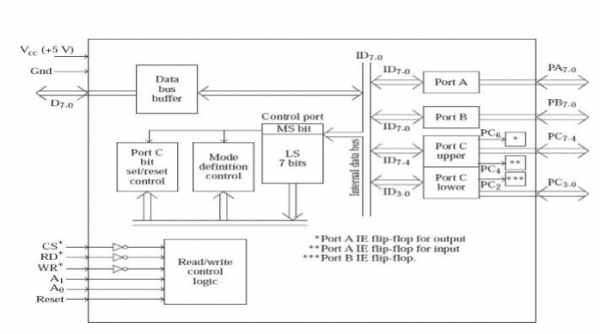

Intel 8255 是一款可编程的周边接口 (PPI) 芯片,用于连接周边设备和接口。我们也称周边设备为输入输出设备。我们使用输入输出端口连接输入输出设备。因此,8255 是一款可编程的输入输出端口芯片。它是一个 40 引脚芯片,采用双列直插式封装。工作电压为 +5 伏直流电。它包含两个 8 位可编程输入输出端口和两个 4 位可编程输入输出端口。我们分别称它们为 A 端口、B 端口、C 端口高位和 C 端口低位。当这些引脚被编程为输出引脚时,它们会在 1.5V 电压下提供 1 mA 的电流。

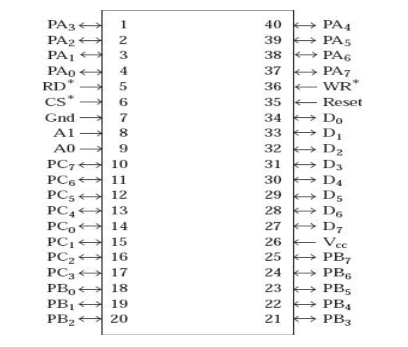

8255 的引脚图如下所示:

我们对 C 端口高位和 C 端口低位进行寻址,使它们构成一个唯一的 8 位端口。因此,我们将 C 端口分成两个 4 位的部分。因此,我们将 C 端口低位编程为输入,C 端口高位编程为输出。

端口选择逻辑如下所示,其中输出由我们设置为逻辑 1,并将其重置为逻辑 0。

8255 有三种工作模式:模式 0、模式 1 和模式 2。我们将模式 0 称为简单输入输出或基本输入输出,用于执行最简单的操作模式。8255 的每个端口都可以编程为在模式 0 下工作。我们将模式 1 称为带应答的输入输出或握手输入输出。当微处理器以不规则的时间间隔向输入设备提供数据时,它非常有用。最后,当处理器读取数据时,端口会通知输入设备处理器已读取数据。

下表显示了 8255 中端口选择是如何完成的。

| A1 | A0 | 所选端口 |

|---|---|---|

| 0 | 0 | A 端口 |

| 0 | 1 | B 端口 |

| 1 | 0 | C 端口 |

| 1 | 1 | 控制端口 |

此外,任何被编程为输出的 C 端口线路都可以使用 C 端口的单比特置位/复位功能设置为逻辑 1 或重置为逻辑 0。此功能减少了基于控制的应用程序中的软件需求。此功能仅适用于 C 端口。此功能还用于启用/禁用来自 8255 端口的中断。

在下表中,我们将讨论 8255 与微处理器的接口:以下描述了 8255 用于与微处理器接口的引脚:

| CS* | 这是 8255 的低电平有效输入引脚。如果此引脚为逻辑 0,则选择 8255 芯片与微处理器通信。如果未选择芯片,则 8255 的数据线 D7-0 将处于高阻态。 |

| D7-0 | 这些引脚是数据引脚,8255 使用它们与微处理器通信。它们连接到微型计算机系统的数据总线上。 |

| RD* | 这是 8255 的低电平有效输入引脚。它连接到 8085 的 RD* 输出。8085 在想要读取 8255 端口中存在的数据时,会激活 8255 的 RD* 输入。 |

| WR* | 这是 8255 的低电平有效输入引脚。它连接到 8085 的 WR* 输出。8085 在想要向 8255 端口写入数据时,会激活 8255 的 WR* 输入。 |

| A1, A0 | 这些是地址输入引脚。它们选择 8255 内的一个端口与微处理器通信。 |

| 复位 | 这是一个高电平有效输入引脚。它连接到 8085 的 ResetOut 输出。它用于复位 8255。复位 8255 后,8255 的所有三个端口都在模式 0(最简单的操作模式)下工作为输入端口。端口的工作模式将在后面介绍。 |

在下表中,我们将讨论 8255 与 I/O 设备的接口:

以下描述了 8255 用于与 I/O 设备接口的引脚。

| PA7-0 | 8255 使用这八个引脚与 I/O 设备通信。如果 A 端口被编程为输出端口,则这些引脚为输出引脚。如果 A 端口被编程为输入操作,则这些引脚为输入引脚。 |

| PB7-0 | 8255 使用这八个引脚与 I/O 设备通信。如果 B 端口被编程为输出端口,则这些引脚为输出引脚。如果 B 端口被编程为输入操作,则这些引脚为输入引脚。 |

| PC7-4 | 8255 使用这四个引脚与 I/O 设备通信。如果 C 端口高位被编程为输出端口,则这些引脚为输出引脚。如果 C 端口高位被编程为输入操作,则这些引脚为输入引脚。 |

| PC3-0 | 8255 使用这四个引脚与 I/O 设备通信。如果 C 端口低位被编程为输出端口,则这些引脚为输出引脚。如果 C 端口低位被编程为输入操作,则这些引脚为输入引脚。 |

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 语言编程

C 语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP