同步计数器设计

在数字电子技术中,一组根据输入脉冲改变状态的触发器被称为数字计数器。在数字计数器电路中,触发器的连接方式使得其在任何时刻的组合状态都是截止到该时刻已发生脉冲总数的二进制等效值。因此,顾名思义,计数器用于计数数字系统中的脉冲。

数字计数器分为以下两种类型:

异步计数器 - 触发器以非同时触发的方式连接的计数器称为异步计数器。异步计数器也称为行波计数器。

同步计数器 - 所有触发器都由同一个时钟脉冲同时触发的计数器称为同步计数器。

在了解计数器的基础知识后,现在让我们讨论同步计数器的设计。

同步计数器设计

同步计数器是一种所有触发器都由相同的时钟脉冲同时触发的计数器。下面解释了同步计数器设计的系统步骤。

步骤 (1) - 确定所需的触发器数量

首先,分析问题描述并确定实现同步计数器所需的触发器数量。如果n是所需的触发器数量,则n的最小值使得状态数N小于或等于2n。

步骤 (2) - 绘制状态图

其次,绘制显示所有可能状态的状态图。状态图基本上是以图形方式表示计数器经过的状态序列。在状态图中,我们还可以包含计数器在下一个时钟脉冲上从无效状态进入特定状态的情况。

步骤 (3) - 选择触发器和激励表

在第三步中,选择特定类型的触发器来实现计数器并绘制其激励表。激励表给出了关于当前状态、下一个状态和触发器所需激励的信息。

步骤 (4) - 获取激励的最小表达式

现在,使用任何最小化技术(例如卡诺图)获得触发器激励的最小表达式。

步骤 (5) - 绘制逻辑图

最后,根据步骤4中获得的最小表达式绘制逻辑电路图。

通过这种方式,我们可以设计一个同步计数器。

同步计数器可能会出现锁存问题,这意味着它们可能无法自启动。自启动计数器是一种同步计数器,无论其初始状态如何,它都将进入其正确的状态序列。我们可以通过设计计数器使其在进入无效状态时进入特定状态来使其自启动。

现在,让我们来看一个例子来理解同步计数器的设计过程。

示例

设计一个使用D触发器的同步计数器,其状态依次为0, 1, 2, 4, 0。未使用的状态必须在下一个时钟脉冲后始终变为零。

解答

此同步计数器按照以下步骤设计:

步骤1 - 所需触发器数量 -

此同步计数器有四个稳定状态,即 0 (000)、1 (001)、2 (010)、4 (100)。但是我们需要三个触发器,因为它也计数到4 (100)。因为三个触发器可以计数八个状态。因此,其余四个状态,即 3 (011)、5 (101)、6 (110) 和 7 (111) 是未使用的状态。根据题意,未使用的状态在下一个时钟脉冲后必须变为 0 (000)。因此,没有无关项。

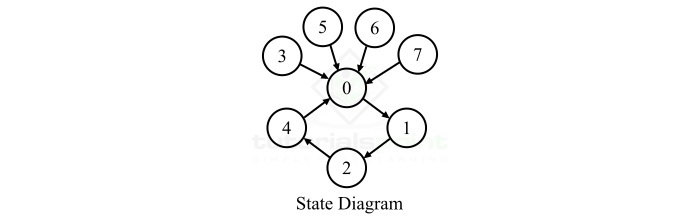

步骤2 - 绘制状态图 -

0, 1, 2, 4, 0, … 计数器的状态图如下所示。

步骤3 - 选择触发器类型并编写激励表 -

使用D触发器,使用D触发器的计数器激励表如下所示。

| 当前状态 | 下一状态 | 所需激励 | ||||||

|---|---|---|---|---|---|---|---|---|

| Q3 | Q2 | Q1 | Q3 | Q2 | Q1 | D3 | D2 | D1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

步骤4 - 推导出最小表达式 -

从激励表中,我们可以看出没有最小化。因此,激励的表达式可以直接从激励表中写出,如下所示:

$$D_{1}=Q_{3}^{'}Q_{2}^{'}Q_{1}^{'}$$

$$D_{2}=Q_{3}^{'}Q_{2}^{'}Q_{1}$$

$$D_{3}=Q_{3}^{'}Q_{2}Q_{1}^{'}+Q_{3}^{'}Q_{2}^{'}Q_{1}$$

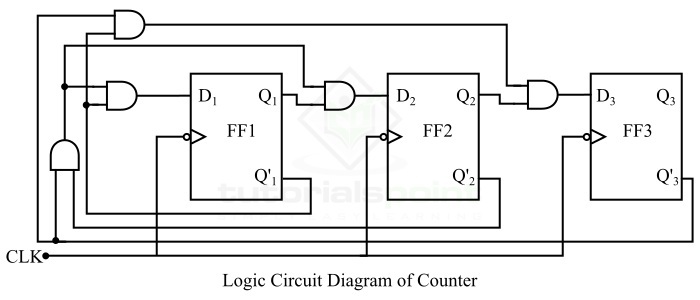

步骤5 - 绘制逻辑电路图 -

根据表达式,0, 1, 2, 4, 0, … 计数器的逻辑电路图如下所示。

这就是关于如何设计同步计数器的全部内容。

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP