边沿触发锁存器

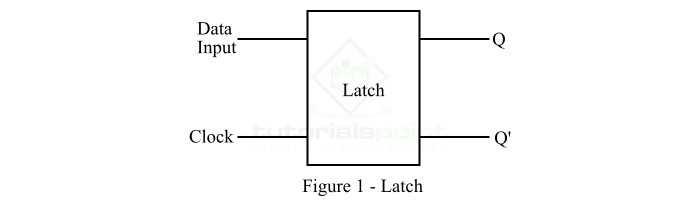

在数字电路中,锁存器是一种具有两个稳定状态的时序逻辑电路。因此,锁存器也被称为双稳态多谐振荡器。锁存器能够存储 1 位信息。锁存器具有一个或多个输入和两个输出。锁存器的输出由 Q 和 Q' 指定。其中,Q 是锁存器的正常输出,Q' 是反相输出。锁存器的框图如图 1 所示。

在本文中,我们将讨论边沿触发锁存器、它们的类型和应用。因此,让我们从边沿触发锁存器的基本定义开始。

什么是边沿触发锁存器?

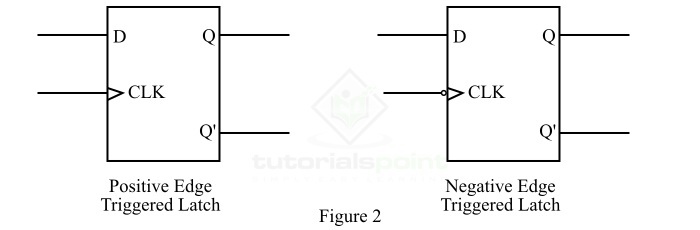

在数字电路中,边沿触发锁存器是一种能够存储 1 位信息的时序电路。它被称为边沿触发锁存器,因为它在时钟脉冲的边沿更新其输出状态。边沿触发锁存器的框图如下面的图 2 所示。

根据锁存器响应的时钟脉冲边沿,边沿触发锁存器可分为以下两种类型:

正边沿触发锁存器

当锁存器在时钟脉冲的正边沿(从低电平到高电平的边沿)捕获并存储输入信息时,称为正边沿触发锁存器。因此,正边沿触发锁存器的输出状态仅在时钟脉冲从低电平转换到高电平时发生变化。

负边沿触发锁存器

当锁存器在时钟脉冲的负边沿(从高电平到低电平的边沿)捕获并存储输入信息时,称为负边沿触发锁存器。因此,负边沿触发锁存器的输出状态仅在时钟脉冲从高电平转换到低电平时发生变化。

边沿触发锁存器的操作

边沿触发锁存器的运行或操作非常简单。边沿触发锁存器包括从输出到输入的反馈路径,以及两个交叉耦合的 NAND 门或 NOR 门。它有两个输入,一个用于数据输入,另一个用于时钟脉冲。

当时钟脉冲为低电平或高电平时,反馈路径断开,锁存器的输出保持其先前状态。当时钟脉冲从低电平变为高电平(或从高电平变为低电平)时,反馈路径闭合,然后根据数据输入的状态确定锁存器的输出状态。

对于正边沿触发锁存器,当时钟脉冲从低电平变为高电平时,锁存器的输出状态根据数据输入发生变化。此输出的新状态在时钟脉冲保持高电平期间保持不变。

对于负边沿触发锁存器,当时钟脉冲从高电平变为低电平时,锁存器的输出状态根据数据输入发生变化。此输出的新状态在时钟脉冲保持低电平期间保持不变。

边沿触发锁存器的优点

边沿触发锁存器的主要优点如下:

边沿触发锁存器可以改善数字电路中的时序控制。

边沿触发锁存器可以降低数字电路中时序违规的风险。

边沿触发锁存器可以提高电路的可靠性。

边沿触发锁存器可以使数字电路不易受噪声信号的影响。

边沿触发锁存器可以降低数字电路输出错误的风险。

边沿触发锁存器消耗的功率相对较少。

边沿触发锁存器可以提高电路的稳定性。

边沿触发锁存器的缺点

边沿触发锁存器的主要缺点如下:

边沿触发锁存器的设计和实现相对复杂。

边沿触发锁存器可以在有限的频率范围内工作。

边沿触发锁存器仅在时钟转换发生时响应。这会导致锁存器的响应延迟。因此,边沿触发锁存器不适用于需要实时响应的场合。

边沿触发锁存器涉及更复杂的时钟管理。

边沿触发锁存器的应用

边沿触发锁存器是多个数字电路中基本的存储单元。边沿触发锁存器的一些常见应用如下:

边沿触发锁存器用于构建寄存器,寄存器用于在数字系统中存储和移位数据。

边沿触发锁存器也用于构建计数器,计数器用于在数字系统中计数事件或周期。

边沿触发锁存器也用于设计存储器单元,如 ROM、RAM 等。

边沿触发锁存器也用作同步数字系统中的关键系统组件。

边沿触发锁存器用于通信系统中,用于数据传输和数据接收的同步。

结论

以上是关于边沿触发锁存器、它们的结构、工作原理、类型和应用的所有内容。总之,边沿触发锁存器是一种专门设计的锁存器,当时钟脉冲从高电平变为低电平或从低电平变为高电平时会响应。它用作多个数字系统中存储 1 位数据的重要组件。

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 语言编程

C 语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP