边沿触发触发器

让我们从简要概述基本触发器开始本文,然后讨论一种特殊的触发器类型,即边沿触发触发器,以及它的工作原理、类型和应用。

什么是触发器?

在数字电子技术中,触发器(FF)是一种时序逻辑电路,用于存储 1 位信息。众所周知,在数字系统中,信息以二进制形式表示,即以 0 和 1 表示。其中,二进制 0 和二进制 1 称为位。

触发器是一个 1 位存储单元,以 0 或 1 的形式存储信息。因此,触发器是所有数字系统中基本的存储单元。

触发器有一个或多个输入和两个输出。其中,一个是正常输出,表示为 Q,另一个是反相输出,表示为 Q'。因此,触发器具有两个稳定状态,因此也称为双稳态多谐振荡器。

典型触发器的逻辑符号图如图 1 所示。

根据对时钟脉冲的响应,触发器分为两种类型,即电平触发触发器和边沿触发触发器。

其操作受连续时钟信号控制,并且当时钟脉冲处于特定电平(高电平或低电平)时其输出状态发生变化的触发器类型称为电平触发触发器。另一方面,当时钟改变其状态时(即从高到低或从低到高)响应的触发器类型称为边沿触发触发器。我们将在本文中更详细地讨论边沿触发触发器。

什么是边沿触发触发器?

能够存储 1 位信息并且仅在时钟脉冲的特定边沿出现时响应的数字电路类型称为边沿触发触发器。

因此,边沿触发触发器的输出状态仅在时钟脉冲的特定边沿出现时更新,即时钟脉冲从低到高或从高到低状态。此触发器不会响应连续的时钟脉冲。

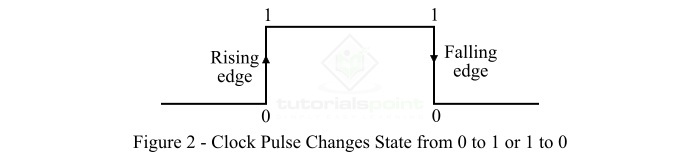

边沿触发触发器用于多个数字电路中,在这些电路中,触发器的输出应在时钟脉冲改变其状态(从 0 到 1 或从 1 到 0)时更新,如图 2 所示。

因此,边沿触发触发器仅在时钟脉冲的上升沿或下降沿工作。

边沿触发触发器的类型

根据时钟脉冲的响应边沿,边沿触发触发器分为两种类型,即

正边沿触发触发器

负边沿触发触发器

正边沿触发触发器

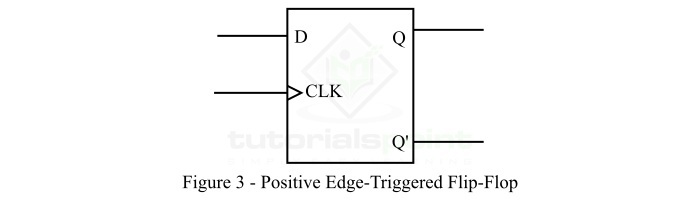

其输出状态仅在时钟脉冲的上升沿(从低到高的边沿)发生变化的边沿触发触发器类型称为正边沿触发触发器。正边沿触发触发器也称为上升沿触发触发器。正边沿触发触发器的框图如下所示(图 3)。

在正边沿触发触发器中,仅当时钟脉冲从低(0)到高(1)时(即在时钟脉冲的上升沿)才接收和存储输入。然后,此存储值在输出端可用。

负边沿触发触发器

其输出状态仅在时钟脉冲的下降沿(从高到低的边沿)发生变化的边沿触发触发器类型称为负边沿触发触发器。负边沿触发触发器也称为下降沿触发触发器。负边沿触发触发器的框图如下所示(图 4)。

对于负边沿触发触发器,触发器仅在时钟脉冲从高到低时(即在时钟脉冲的下降沿)捕获和存储输入。

边沿触发触发器的工作原理

典型边沿触发触发器的工作原理如下:

在边沿触发触发器中,输入通过输入端应用,并且时钟脉冲连接到触发器的时钟输入。当时钟脉冲从低到高或从高到低时,边沿触发触发器根据应用的输入做出响应。当发生时钟脉冲的这种状态转换时,触发器捕获并存储输入值。然后,这些存储的输入值将在触发器的输出端(Q 和 Q')可用。

边沿触发触发器的优点

边沿触发触发器的主要优点如下:

与电平触发触发器相比,边沿触发触发器具有改进的时序行为。这是因为边沿触发触发器仅在时钟脉冲转换时响应。

边沿触发触发器减少了可能导致系统错误的毛刺。

边沿触发触发器的功耗比电平触发触发器低。

边沿触发触发器的电路设计相对简单。

边沿触发触发器可以轻松地集成到数字 IC 的形式中。

边沿触发触发器在具有非常高时钟速度的数字系统中非常有用。

边沿触发触发器的应用

边沿触发触发器用于各种数字系统中。边沿触发触发器的一些常见应用包括:

边沿触发触发器用于寄存器中,以在数字电路的不同部分之间存储和传输二进制信息。

边沿触发触发器用于数字计数器中,以生成二进制值的序列。

边沿触发触发器也用于数字信号处理。

边沿触发触发器用于需要时序和信号同步的多个数字应用中。

边沿触发触发器还用于构建 ROM、RAM 等的存储单元,以在数字系统中存储二进制数据。

结论

这就是关于边沿触发触发器的所有内容。总之,边沿触发触发器是许多数字系统(如存储器、寄存器、计数器等)的重要构建块之一。

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP