主从JK触发器

JK触发器是一种具有J和K两个输入端、一个时钟输入端以及由Q和Q'指定的两个输出端的1位存储单元。JK触发器是SR触发器的改进版本,它没有禁状态。为了避免禁状态或不确定状态,JK触发器的输出反馈到其输入端。

然而,由于这些反馈路径,电路中出现了一个新的问题,称为竞争冒险。JK触发器中的竞争冒险是一个主要问题,其中触发器的输出会持续切换,直到施加的时钟信号结束。

为了避免JK触发器中的竞争冒险问题,我们使用主从模式的JK触发器。因此,JK触发器被称为主从触发器。

因此,让我们从主从JK触发器的基本结构开始。

什么是主从JK触发器?

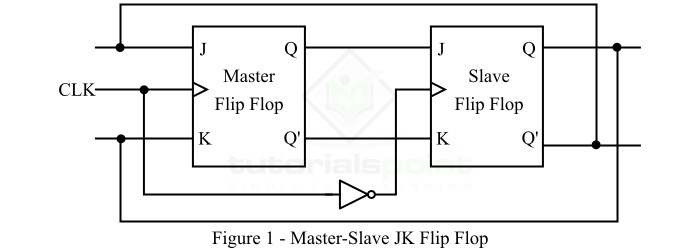

主从JK触发器是由两个级联连接的JK触发器组成的组合,如图1所示。

在这两个JK触发器的组合中,一个充当主触发器,另一个充当从触发器。在这个主从触发器中,主JK触发器的输出连接到从JK触发器的输入端。从触发器的输出反馈到主JK触发器的输入端。

在主从JK触发器中,还使用了一个非门(反相器),它以反相时钟信号被施加到从触发器的方式连接到时钟信号。

因此,当主触发器的时钟信号为0时,从触发器的时钟信号为1;如果主触发器的时钟信号为1,则从触发器的时钟信号为0。

主从JK触发器的操作

当时钟脉冲变为高电平时,从触发器变为非活动状态,并且输入J和K可以控制系统的状态。

当时钟脉冲回到低电平时,信息从主触发器转移到从触发器,并获得系统的最终输出。

从电路可以看出,主触发器是正电平触发的,从触发器是负电平触发的。因此,主触发器在从触发器之前响应。现在,让我们讨论主从JK触发器在不同输入组合J和K下的操作。

当J = 0且K = 0时,两个JK触发器都保持非活动状态,因此输出Q保持不变。这称为主从JK触发器的保持状态。

当J = 0且K = 1时,主触发器的输出Q'为高电平,并进入从触发器的输入K。时钟信号迫使从触发器复位。因此,从触发器具有与主触发器相同的输出,即高Q'和低Q。这称为主从JK触发器的复位状态。

当J = 1且K = 0时,主触发器的输出Q为高电平,并进入从触发器的输入J,时钟信号的负跳变置位从触发器。因此,这称为主从JK触发器的置位状态。

当J = 1且K = 1时,对于这种输入组合,主触发器在时钟脉冲的正跳变时切换,从触发器在时钟脉冲的负跳变时切换。因此,解决了JK触发器竞争冒险的问题。

主从JK触发器的真值表

以下是主从JK触发器的真值表:

| 输入 | 输出 | 注释 | |

|---|---|---|---|

| J | K | Qn+1 | |

| 0 | 0 | Qn | 无变化 |

| 0 | 1 | 0 | 复位 |

| 1 | 0 | 1 | 置位 |

| 1 | 1 | Qn' | 翻转 |

这就是关于主从JK触发器及其操作的全部内容。

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP