8251 USART与8085微处理器接口

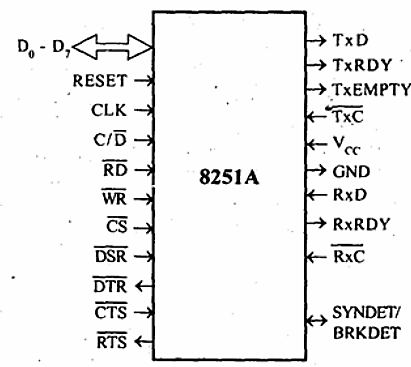

8251芯片是通用同步异步收发器(USART)。它充当微处理器和外围设备之间的中介。它将串行数据转换为并行形式,反之亦然。该芯片是28引脚DIP。

8251A芯片的引脚说明

| 引脚 | 描述 |

|---|---|

| D0 - D7 | 并行数据 |

| C/D | 控制寄存器或数据缓冲区选择 |

| RD | 读控制 |

| WR | 写控制 |

| CS | 片选 |

| CLK | 时钟脉冲 |

| RESET | 复位 |

| TxC | 发送器时钟 |

| TxD | 发送数据 |

| RxC | 接收器时钟 |

| RxD | 接收数据 |

| RxRDY | 接收器就绪 |

| TxRDY | 发送器就绪 |

| DSR | 数据设备就绪 |

| DTR | 数据终端就绪 |

| SYNDET/ | 同步检测/ |

| BRKDET | 中断检测 |

| RTS | 请求发送数据 |

| CTS | 允许发送数据 |

| TxEMPTY | 发送器空闲 |

| Vcc | Vcc (5V) |

| GND | 接地(0V) |

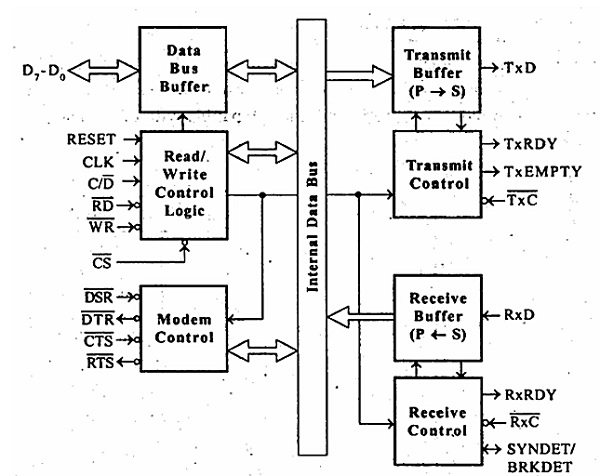

现在让我们看看8251芯片的功能框图。

该图中有五个不同的部分。这些部分如下:

读/写控制逻辑

发送器

接收器

数据总线缓冲器

调制解调器控制。

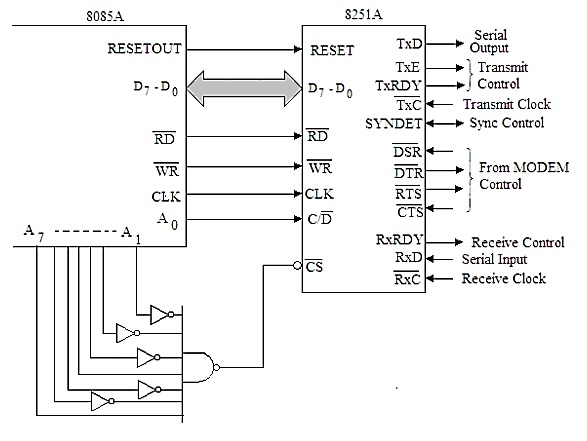

8251与8085接口

现在让我们看看如何将8251与8085接口。在图中,我们可以看到8条数据线D7-0连接到微处理器的地址总线。并且8251的RD和WR也分别连接到8051的RD和RD。8251从8085的CLK OUT引脚获取时钟。复位引脚也连接到微处理器的RESET OUT引脚。

C/D 引脚用于选择控制寄存器或数据寄存器。此引脚连接到8085的A0引脚。8251的CS引脚连接到地址解码器电路的输出。地址解码器使用微处理器的A7 到A1线。在这个图中,当A7和A4为逻辑1,所有其他线为逻辑0时,CS将被启用。

从下表中,我们可以看到如何读取或写入数据字、读取状态字和写入控制字。

| A0 | RD | WR | 任务 | 端口地址 |

|---|---|---|---|---|

| 0 | 0 | 1 | 读取数据字 | 90H |

| 0 | 1 | 0 | 写入数据字 | 90H |

| 1 | 0 | 1 | 读取状态字 | 91H |

| 1 | 1 | 0 | 写入控制字 | 91H |

广告

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP