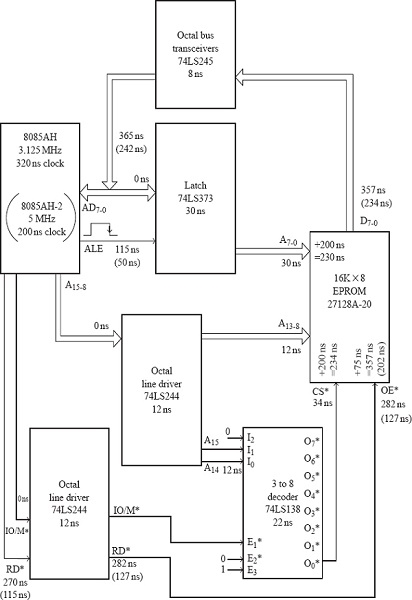

27128-20 与 8085 微处理器中 8085AH 的兼容性检查

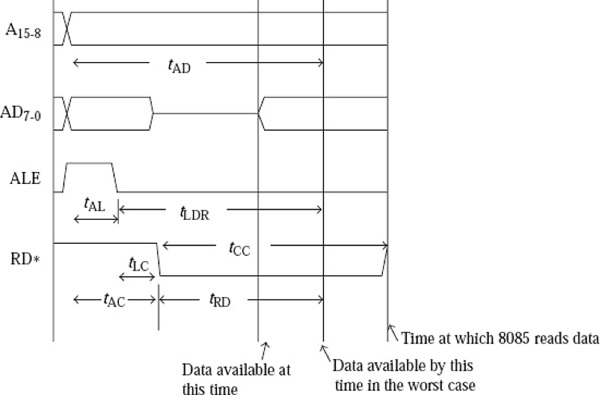

让我们根据tAD、tLDR 和tRD 参数执行内存兼容性检查。

关于tAD的兼容性:地址从 A15 到 A0 的有效地址与地址从 AD7 到 AD0 的有效数据之间的时间间隔。对于 8085AH,T 状态工作时间为 320 nS,但最多可达 575 nS。但此处有效数据可用时间为 365 nS。因此,内存速度是兼容的,并且有 575 nS - 365 nS = 210 nS 的额外时间裕度。

关于tLDR的兼容性:算术逻辑单元尾随边沿与地址从 AD7 到 AD0 的有效数据之间的时间间隔,读取操作。对于工作在 320 nS T 状态的 8085AH,最大值为 460 nS。ALE 的尾随边沿出现在 115 nS。因此,在这种情况下,tLDR 仅为 365 nS - 115 nS = 250 nS。因此,内存速度是兼容的,实际上有 460 nS - 250 nS = 210 nS 的额外时间裕度。

关于tRD的兼容性:RD* 的前沿与地址相当于 AD7-0 的有效数据之间的时间间隔。对于工作在 320 nS T 状态的,需要最大 300 nS。RD* 信号由 8085 AH 在 270 nS 激活,并由其在 365 nS 提供有效数据。

因此,27128-20 EPROM 芯片的速度与 8085AH 兼容。因此,8085AH 与内存芯片接口,这些芯片具有如下所示的最坏情况规格

tAcc = 327 nS + 205 nS = 532 nS

tCE = 323 nS + 205 nS = 528 nS

tOE = 75 nS + 205 nS = 280 nS

在 ALS 套件中访问 27128 EPROM 所涉及的延迟。

MR 机器周期总线时序特性

广告

数据结构

数据结构 网络

网络 关系数据库管理系统

关系数据库管理系统 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 编程

C 编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP