- 8085 微处理器

- 微处理器 - 8085 架构

- 8085 引脚配置

- 寻址模式和中断

- 8085 指令集

- 多处理器配置

- 配置概述

- 8087 数值数据处理器

- I/O 接口

- I/O 接口概述

- 8279 可编程键盘

- 8257 DMA 控制器

- 微处理器有用资源

- 微处理器 - 快速指南

- 微处理器 - 有用资源

- 微处理器 - 讨论

Intel 8253 - 可编程间隔定时器

Intel 8253 和 8254 是可编程间隔定时器 (PTI),专为微处理器设计,使用三个 16 位寄存器执行计时和计数功能。每个计数器有两个输入引脚,即时钟和门,还有一个“OUT”输出引脚。要操作计数器,需要在其寄存器中加载一个 16 位计数。根据命令,它开始递减计数,直到达到 0,然后它生成一个脉冲,可用于中断 CPU。

8253 和 8254 的区别

下表区分了 8253 和 8254 的特性:

| 8253 | 8254 |

|---|---|

| 其工作频率为 0 - 2.6 MHz | 其工作频率为 0 - 10 MHz |

| 它使用 N-MOS 技术 | 它使用 H-MOS 技术 |

| 不支持读回命令 | 支持读回命令 |

| 不能交错读取和写入同一个计数器。 | 可以交错读取和写入同一个计数器。 |

8253/54 的特性

8253/54 最突出的特性如下:

它具有三个独立的 16 位向下计数器。

它可以处理从 DC 到 10 MHz 的输入。

这三个计数器可以编程为二进制或 BCD 计数。

它几乎兼容所有微处理器。

8254 有一个强大的命令,称为读回命令,允许用户检查计数值、编程模式、当前模式和计数器的当前状态。

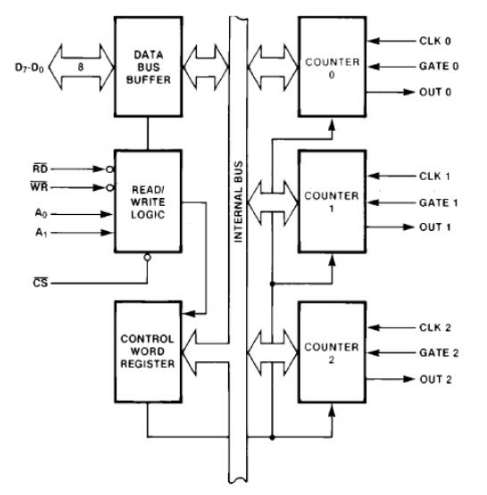

8254 架构

8254 的架构如下:

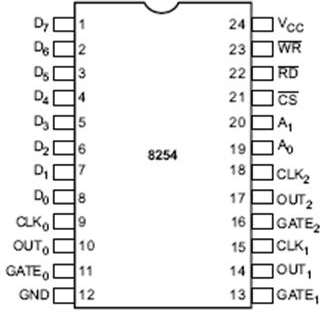

8254 引脚描述

以下是 8254 的引脚图:

在上图中,有三个计数器、一个数据总线缓冲器、读/写控制逻辑和一个控制寄存器。每个计数器有两个输入信号 - 时钟和门,以及一个输出信号 - OUT。

数据总线缓冲器

它是一个三态、双向、8 位缓冲器,用于将 8253/54 接口到系统数据总线。它具有三个基本功能:

- 编程 8253/54 的模式。

- 加载计数寄存器。

- 读取计数值。

读/写逻辑

它包括 5 个信号,即 RD、WR、CS 和地址线 A0 & A1。在外设 I/O 模式下,RD 和 WR 信号分别连接到 IOR 和 IOW。在存储器映射 I/O 模式下,这些连接到 MEMR 和 MEMW。

CPU 的地址线 A0 & A1 连接到 8253/54 的 A0 和 A1 线,CS 连接到解码地址。控制字寄存器和计数器根据 A0 & A1 线上的信号进行选择。

| A1 | A0 | 结果 |

|---|---|---|

| 0 | 0 | 计数器 0 |

| 0 | 1 | 计数器 1 |

| 1 | 0 | 计数器 2 |

| 1 | 1 | 控制字寄存器 |

| X | X | 无选择 |

控制字寄存器

当 A0 & A1 线为逻辑 1 时访问此寄存器。它用于写入命令字,该命令字指定要使用的计数器、其模式以及读或写操作。下表显示了各种控制输入的结果。

| A1 | A0 | RD | WR | CS | 结果 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 写入计数器 0 |

| 0 | 1 | 1 | 0 | 0 | 写入计数器 1 |

| 1 | 0 | 1 | 0 | 0 | 写入计数器 2 |

| 1 | 1 | 1 | 0 | 0 | 写入控制字 |

| 0 | 0 | 0 | 1 | 0 | 读取计数器 0 |

| 0 | 1 | 0 | 1 | 0 | 读取计数器 1 |

| 1 | 0 | 0 | 1 | 0 | 读取计数器 2 |

| 1 | 1 | 0 | 1 | 0 | 无操作 |

| X | X | 1 | 1 | 0 | 无操作 |

| X | X | X | X | 1 | 无操作 |

计数器

每个计数器由一个单一的 16 位向下计数器组成,可以以二进制或 BCD 方式操作。其输入和输出由控制字寄存器中存储的模式选择配置。程序员可以读取任何三个计数器的内容,而不会影响正在进行的实际计数。