什么是通用寄存器组织?

一组触发器构成一个寄存器。寄存器是CPU中独特的、高速的存储区域。它们包括实现数据处理的组合电路。在处理之前,信息始终在寄存器中定义。寄存器加快了程序的执行速度。

寄存器在 CPU 操作中实现两个重要的功能,如下所示:

- 它可以为数据提供临时存储位置。这支持直接实现程序,以便在需要时快速访问数据。

- 它可以保存 CPU 的状态和有关直接实现程序的数据。

示例 - 下一个程序指令的地址、来自外部设备的信号和错误消息,以及包括不同的数据都保存在寄存器中。

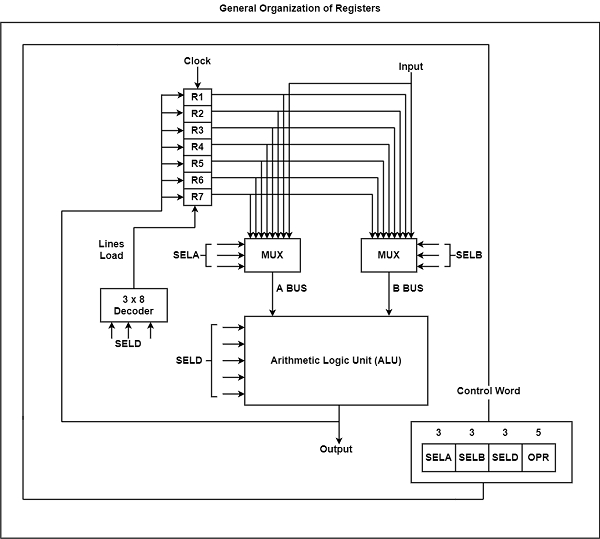

如果 CPU 包含一些寄存器,则一个公共总线可以连接这些寄存器。图中显示了七个 CPU 寄存器的通用组织结构。

CPU 总线系统由控制单元管理。控制单元通过选择 ALU 的功能和系统的组件来明确数据流经算术逻辑单元 (ALU)。

考虑 R1 ← R2 + R3,以下是在 CPU 内实现的功能:

MUX A 选择器 (SELA) - 它可以将 R2 放入总线 A。

MUX B 选择器 (SELB) - 它可以将 R3 放入总线 B。

ALU 操作选择器 (OPR) - 它可以选择算术加法 (ADD)。

解码器目标选择器 (SELD) - 它可以将结果传输到 R1。

三态门的复用器由总线执行。14 个二进制选择输入的状态决定了控制字。14 位控制字定义了一个微操作。

寄存器选择字段的编码在表中指定。

寄存器选择字段的编码

| 二进制代码 | SELA | SELB | SELD |

|---|---|---|---|

| 000 | 输入 | 输入 | 无 |

| 001 | R1 | R1 | R1 |

| 010 | R2 | R2 | R2 |

| 011 | R3 | R3 | R3 |

| 100 | R4 | R4 | R4 |

| 101 | R5 | R5 | R5 |

| 110 | R6 | R6 | R6 |

| 111 | R7 | R7 | R7 |

ALU 实现了一些微操作。表中显示了 ALU 实现的一些操作。

ALU 操作的编码

| OPR 选择 | 操作 | 符号 |

|---|---|---|

| 00000 | 传输 A | TSFA |

| 00001 | 递增 A | INCA |

| 00010 | 加 A + B | ADD |

| 00101 | 减 A - B | SUB |

| 00110 | 递减 A | DECA |

| 01000 | A 和 B 相加 | AND |

| 01010 | A 和 B 或运算 | OR |

| 01100 | A 和 B 异或运算 | XOR |

| 01110 | A 的补码 | COMA |

| 10000 | 右移 A | SHRA |

| 11000 | 左移 A | SHLA |

表中显示了一些 ALU 微操作。

ALU 微操作

| 微操作 | SELA | SELB | SELD | OPR | 控制字 | |||

| R1 ← R2 – R3 | R2 | R3 | R1 | SUB | 010 | 011 | 001 | 00101 |

| R4 ← R4 ∨ R5 | R4 | R5 | R4 | OR | 100 | 101 | 100 | 01010 |

| R6 ← R6 + R1 | - | R6 | R1 | INCA | 110 | 000 | 110 | 00001 |

| R7 ← R1 | R1 | - | R7 | TSFA | 001 | 000 | 111 | 00000 |

| 输出 ← R2 | R2 | – | 无 | TSFA | 010 | 000 | 000 | 00000 |

| 输出 ← 输入 | 输入 | - | 无 | TSFA | 000 | 000 | 000 | 00000 |

| R4 ← shl R4 | R4 | - | R4 | SHLA | 100 | 000 | 100 | 11000 |

| R5 ← 0 | R5 | R5 | R5 | XOR | 101 | 101 | 101 | 01100 |

广告

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 编程

C 编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP