计算机体系结构中内存子系统的配置是什么?

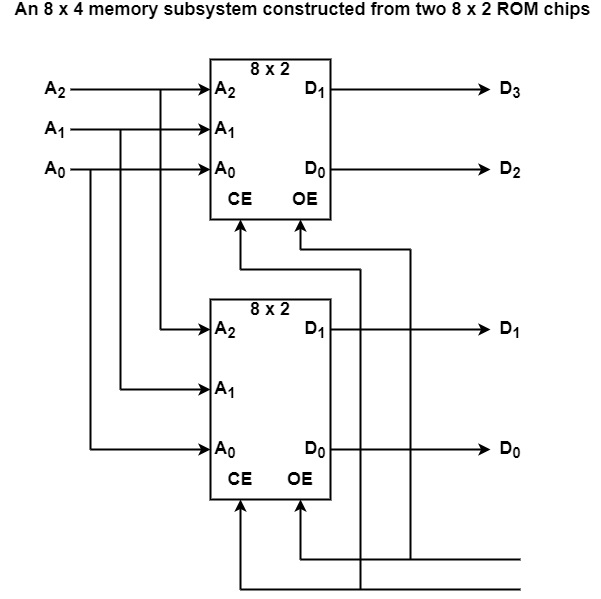

以下技术用于将内存芯片连接起来形成内存子系统。可以组合两个或多个芯片来生成具有更多位/位置的内存。这是通过连接芯片的相应地址和控制信号以及将其数据引脚连接到数据总线的各个位来实现的。

例如,可以将两个 8 x 2 芯片组合成一个 8 x 4 内存,如图所示。两个芯片都从总线接收相同的三个地址输入,以及相同的芯片使能和输出使能信号。

第一个芯片的数据芯片连接到数据总线的第 3 位和第 2 位,而另一个芯片的数据芯片连接到第 1 位和第 0 位。当 CPU 读取数据时,它会在地址总线上定位地址。两个芯片都在地址位 A2、A1 和 A0 上读取,并执行其内部解码。

如果 CE 和 OE 信号被激活,芯片会将其数据输出到数据总线的四位上。由于两个芯片的地址和使能信号相同,因此在任何给定时间,两个芯片都处于活动状态或都不处于活动状态。该设备永远不会只有一个处于活动状态。因此,它们至少在 CPU 关注的情况下,作为一个单一的 8 x 4 芯片发挥作用。

除了生成更宽的字之外,还可以将芯片组合起来以生成更多字。类似的两个 8 x 2 芯片可以配置为 16 x 2 内存子系统。上部芯片配置为内存位置 0 到 7(0000 到 0111),下部芯片配置为位置 8 到 15(1000 到 1111)。

上部芯片始终具有 A3=0,而下部芯片具有 A3=1。此差异可以选择两个芯片之一。当 A3=0 时,上部芯片被使能,下部芯片被禁用。输出使能可以连接起来,因为只有被使能的芯片才能输出数据。两个芯片对应于相同的数据位,都连接到数据总线的 D1 和 D0。

这种配置使用高阶交错。芯片内的所有内存位置在系统内存中都是连续的。考虑图 (b) 中显示的配置,该配置使用低阶交错。当 A0=0 时,或在地址 XXX0 时,上部芯片被使能,在这种情况下,为 0、2、4、6、8、10、12 和 14。当 A0=1 时,下部芯片被使能,这对于地址 1、3、5、7、9、11、13 和 15 是正确的。

数据结构

数据结构 网络

网络 关系数据库管理系统

关系数据库管理系统 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 编程

C 编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP