什么是调度率?

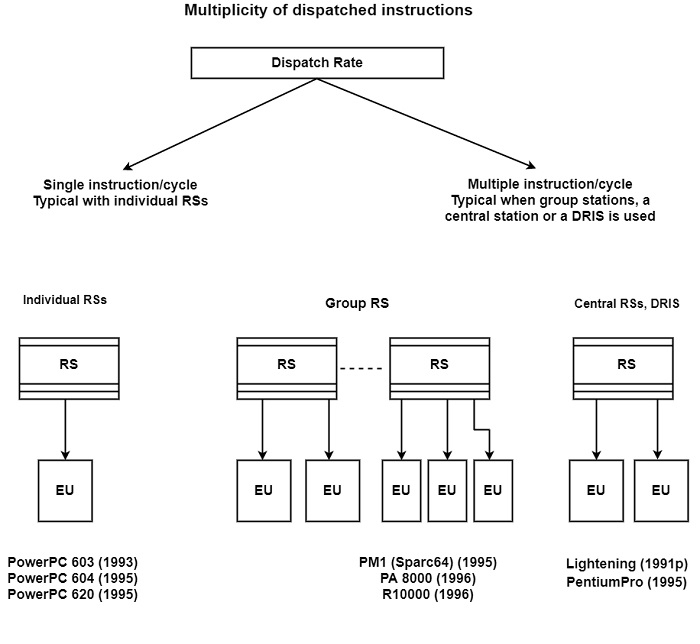

与单独的预留站不同,组预留站或中央预留站(或 DRIS)必须能够高效地调度每个周期多于一条指令。在这些情况下,设计空间需要一个额外的组件来确定每个预留站或 DRIS 每个周期可以调度多少条指令。这个组件被称为**调度率**。

一个搁置缓冲区必须能够在每个周期内将一条指令调度到连接到它的任何执行单元 (EU)。对于具有两到三个 EU 的组站来说,这更容易实现,而对于连接有相当数量 EU 的中央站或 DRIS 来说,则比较困难。例如,R10000 使用组预留站。它的 FX 预留站每个周期可以调度两条指令,每条指令分别发往所服务的 EU。

相反,它的 FP 预留站服务于四个 FP EU,但每个周期最多只能调度两条指令。一条指令可以转发到 FP 加法器,另一条可以转发到 FP 乘法器、FP 除法器或 FP 平方根单元。这些调度率限制主要是由于数据路径或寄存器端口的限制,目的是降低复杂性。

对于中央预留站或 DRIS,需要的调度率高于组站。例如,PentiumPro 每个周期可以调度五条 RISC 指令(称为 nop-s)。需要注意的是,端口 0 由六个 EU 共享。这是一个设计权衡。在 PentiumPro 中,FP 数据内部需要 86 位。考虑到每个 FP 单元至少需要两个操作数并至少提供一个结果,通过共享一个复杂的输入/输出端口可以在芯片面积上节省相当大的空间。

如表所示,具有搁置功能的超标量处理器的最大指令发布和调度率。

具有搁置功能的超标量处理器的最大指令发布和调度率

| 处理器/批量发货年份 | 最大指令发布率 (指令/周期) | 最大调度率 (指令/周期) |

|---|---|---|

| PowerPC 603 (1993) | 3 | 3 |

| PowerPC 604 (1995) | 4 | 6 |

| PowerPC 620 (1995) | 4 | 6 |

| Power2 (1993) | 4/6 | 10 |

| Nx586 (1994) | ¾ | ¾ |

| K5 (1995) | 4 | 5 |

| PentiumPro (1995) | 4 | 5 |

| PM1 (Sparc 64) (1995) | 4 | 8 |

| PA8000 (1996) | 4 | 4 |

| R10000 (1996) | 4 | 5 |

如表所示,在某些情况下,这两个比率相同,例如在 PowerPC 603 和 PA 8000 处理器中。在大多数情况下,具有搁置功能的超标量处理器能够调度更多指令执行,而不是将其发布到搁置区。例如,PowerPC 604 和 PowerPC 620 最多可以发布四条指令,但在每个周期内最多可以启动六个操作的执行。

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP