计算机体系结构中的加载/存储重排序是什么?

加载和存储指令涉及影响处理器和内存的操作。在执行过程中,加载和存储都必须首先等待其地址由算术逻辑单元 (ALU) 或地址单元计算。然后,加载可以访问数据缓存以获取请求的内存数据,然后将其提供给寄存器。然后,加载通常通过将获取的数据写入指定的体系结构寄存器来完成。

存储具有不同的执行模式。在接收到生成的地址后,存储必须等待其操作数可用。与其他指令不同,存储在操作数可用时即被认为已完成。现在让我们考虑一下正在使用的 ROB。当 ROB 指示存储在顺序执行中接下来执行时,将要存储的内存地址和数据被转发到缓存,并启动缓存存储操作。

支持弱内存一致性的处理器允许内存访问的重排序。这至少对三种方法有利:

- 它允许加载/存储旁路。

- 它创建可实现的推测性加载或存储

- 它使缓存未命中保持隐秘

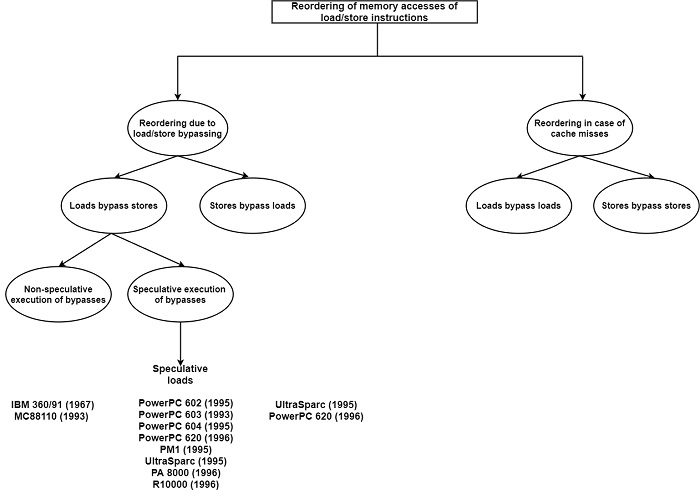

加载/存储旁路意味着加载可以绕过挂起的存储,反之亦然,前提是不违反内存数据依赖性。如图所示,几个最近的处理器允许加载绕过存储,但反之则不行。

允许加载绕过存储的优点是可以允许紧密循环的运行时重叠。通过允许迭代开始时的加载访问内存而无需等待前一次迭代结束时的存储完成,可以实现重叠。它可以避免获取错误的数据值,只有当之前的存储与加载的目标地址不相同时,加载才能绕过挂起的存储。

对此情况更高级的处理是让加载推测性地绕过存储,也就是说,允许推测性加载。推测性加载避免将内存访问延迟到所有必需的地址都已计算并且可以排除冲突的地址为止。

地址检查通常通过将加载和存储的计算目标地址写入 ROB 或 DRIS 并在此处执行地址比较来执行。它可以降低所需电路的复杂性,地址检查通常仅限于完整有效地址的一部分。

缓存未命中是性能障碍的另一个来源,可以通过加载/存储重排序来减少。缓存未命中会导致所有后续相同类型的操作阻塞。

广告

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 语言编程

C 语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP