什么是 BTIC 方案?

此方案仅在因指令缓存延迟过长而导致的惩罚过高时才会偶尔使用。BTIC 方案的基本思想是提供一个小的额外缓存,对于已执行或预测已执行的分支,它提供分支目标指令或指定数量的 BTI,而不是 BTA。因此,可以利用原本未使用的流水线周期来执行目标指令。

BTIC 方案有两种替代实现方式,如图所示。在第一种方式中,已执行路径的延续地址也存储在 BTIC 中,而在第二种方式中,它是动态计算的。

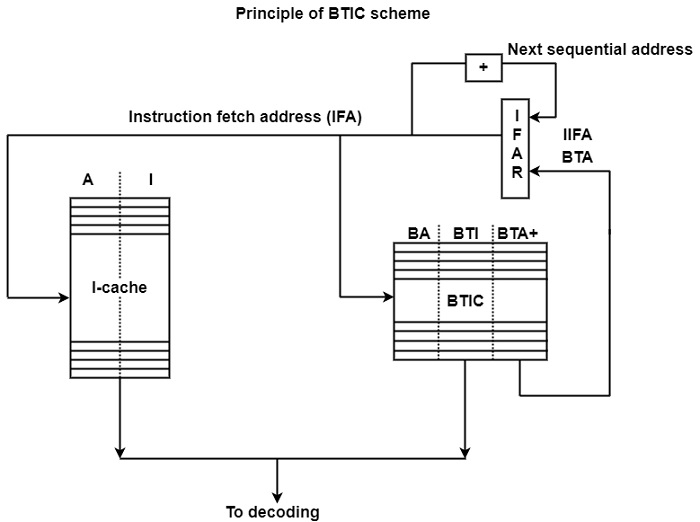

存储已执行路径延续的 BTIC 方案 - 此实现的原理基于 Hitachi Gmicro/200 (1988) 处理器,如图所示。Gmicro 系列处理器是在 1984 年启动的日本 TRON 项目框架内开发的。TRON 是一种在某些层面上定义的开放式架构,包括 ISA 层 (Sakamura, 1987a, 1987b)。

TRON ISA 是一种 CISC 架构。Gmicro/200 是第一个实现 TRON ISA 规范的微处理器。它是一个使用六阶段 CISC 流水线和加载延迟为两个周期的指令缓存的标量实现。

如图所示,BTIC 包含由三个组成部分组成的条目。它们是当前已执行分支的地址 (BA)、分支目标指令 (BTI) 和 BTI 后面的指令的地址 (指定为 BTA+)。

当 BTIC 中存在实际指令提取地址 (IFA) 的条目时,BTI 将从 BTIC 中提取,并且选择此指令进行解码,而不是直接从指令缓存中读取指令。沿着已执行路径的后续指令的地址 (BTA+) 也从 BTIC 中提取。它成为下一个 BTA。BTIC 只包含四个条目。

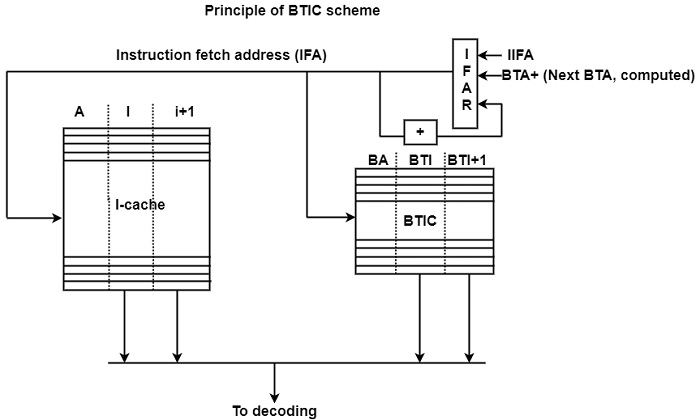

计算已执行路径延续的 BTIC 四方案 - BTIC 方案的另一个变体不同之处在于,已执行路径延续的地址是计算出来的,而不是存储在 BTIC 中并从中读取。该图通过展示它在 MC 88110 处理器中的实现方式来演示这一点。

BTIC 包括当前已执行分支的最终地址 (BA) 三元组以及相应分支目标路径的前两条指令 (BTI 和 BTI + 1)。

当 BTIC 包含实际 IFA 的条目时,相应的两个目标指令 (BTI 和 BTI + 1) 将从 BTIC 中提取并选择进行解码,而不是从指令缓存中读取两个连续的指令。已执行路径延续的地址 (BTA+) 通过增量从 BTA 计算得出,并用作下一个 IFA。

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 编程

C 编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP