什么是垂直微代码?

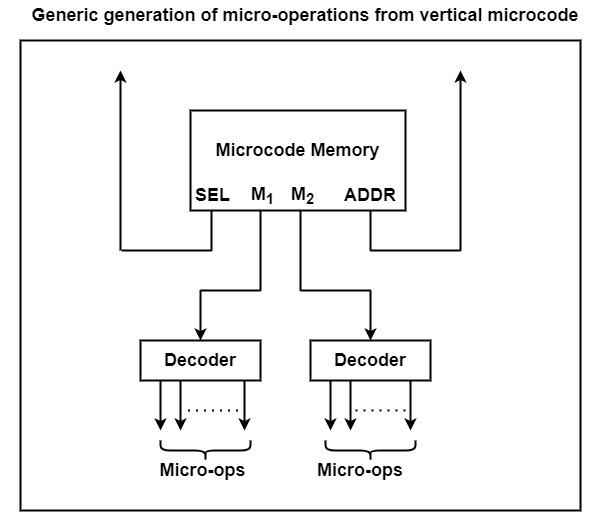

在垂直微代码中,每条微指令都被编码,即位字段可以穿过中间组合逻辑,进而产生内部 CPU 组件(ALU、寄存器等)的实际控制信号。在垂直微代码中,微操作被分组到字段中,使得在任何状态下,一个字段中最多只有一个微操作处于活动状态。然后,为字段中的每个微操作分配一个唯一的字段值。

例如,一个具有八个不同微操作的字段需要 3 位,从 000 到 111 的每个值都将分配给八个微操作之一。微操作字段位从微代码存储器输出到解码器。解码器的输出是水平微代码下直接生成的微操作。

每当在相似状态下出现两个微操作时,将它们分配到多个字段。每个字段在一个周期内只能输出一个微操作的值。如果两个微操作要同时发生,它们不能在同一个字段中。

如果重要的话,每个字段都包含一个 NOP。可能某些状态不需要激活给定字段中的任何微操作。如图所示,即使没有激活微操作,也必须从微代码存储器输出一些值。这可以通过分配剩余的微操作来实现微操作字段位的最佳利用。设计者应该尝试最佳利用字段位。例如,具有五个、六个、七个或八个微操作(包括 NOP)的字段需要 3 位。

将更改相似寄存器的微操作分组到相同的字段中。因为两个微操作不能同时修改同一个寄存器,所以可以将它们放在同一个微操作字段中。

将更改相似寄存器的微操作分组到相同的字段中。因为两个微操作不能同时修改同一个寄存器,所以可以将它们放在同一个微操作字段中。

M1 M2 NOP NOP DRM PCIN

因为 PCIN 和 PCDR 都更改 PC,所以可以将 PCDR 添加到 M2。接下来,可以任意地将剩余的微操作分配到字段中,并将更改相似寄存器的微操作保存在相同的字段中。有一种可能的情况会产生以下分配。

M1 M2 NOP NOP DRM PCIN ACIN PCDR PLUS ARPC AND AIDR

每个字段有五个微操作,因此每个字段需要 3 位,总共 6 位。通过调整分配可以减少总位数。只需将 AIDR 从 M2 移动到 M1,就可以将 M1 和 M2 中的微操作数量分别从 5 和 5 更改为 6 和 4。M1 需要 3 位,但 M2 只需要 2 位。每个微代码字将少一位。

数据结构

数据结构 网络

网络 关系数据库管理系统 (RDBMS)

关系数据库管理系统 (RDBMS) 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言编程

C语言编程 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP