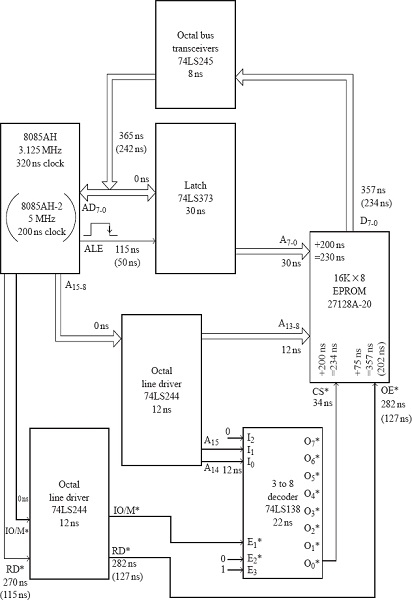

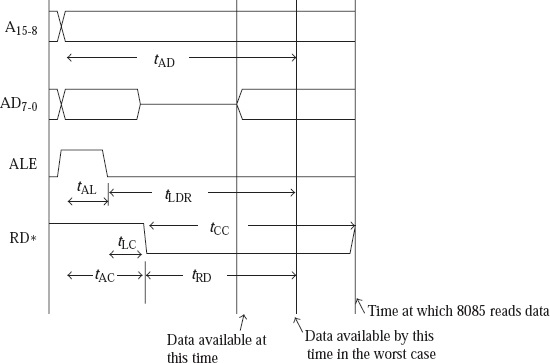

考虑8085微处理器的TOE时的最早数据输出时间

8085AH在270ns时激活RD*信号。该信号通过八进制线路驱动器74LS241延迟12ns后移动到27128的OE*引脚。因此,OE*信号在282ns末尾被27128接收到。因此,数据只能在282ns+tOE=282ns+75ns+357ns内从小于27128的D7 到D0引脚输出。

从之前的讨论中可以清楚地看出,考虑到三个参数tACC、tCE和tOE,最早的数据输出时间应为357ns。此外,tAcc可以是200ns+(357ns–230ns)等于327ns,而不会影响数据从存储芯片输出的时间。同样,tCE可以大到200ns+(357ns–234ns),等于323ns,而不会影响数据从存储芯片释放的时间。

通过八进制总线收发器74LS245以8ns的时延从27128接收数据。因此,8085AH在357ns+8ns等于365ns时接收到有效数据。

广告

数据结构

数据结构 网络

网络 RDBMS

RDBMS 操作系统

操作系统 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C语言程序设计

C语言程序设计 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP