- 基础电子学教程

- 基础电子学 - 首页

- 电感器

- 基础电子学 - 电感器

- 基础电子学 - 电感

- 电感器的电路连接

- 电感器的类型

- 基础电子学 - 射频电感器

- 基础电子学有用资源

- 基础电子学 - 快速指南

- 基础电子学 - 有用资源

- 基础电子学 - 讨论

基础电子学 - 场效应晶体管(JFET)

JFET是结型场效应晶体管的缩写。JFET就像普通的场效应晶体管一样。JFET的类型有N沟道FET和P沟道FET。在N沟道FET中,P型材料添加到N型衬底上,而在P沟道FET中,N型材料添加到P型衬底上。因此,理解其中一种FET就足以理解两种FET。

N沟道FET

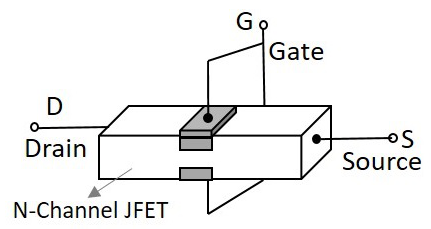

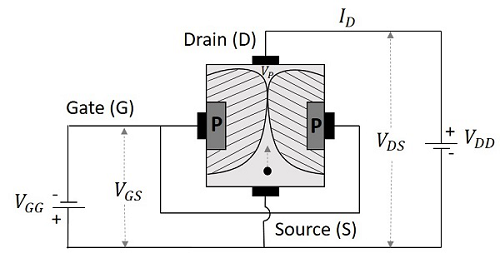

N沟道FET是最常用的场效应晶体管。为了制造N沟道FET,取一根窄的N型半导体棒,在其相对两侧通过扩散形成P型材料。这两侧连接在一起,形成栅极终端的单个连接。这可以从下图理解。

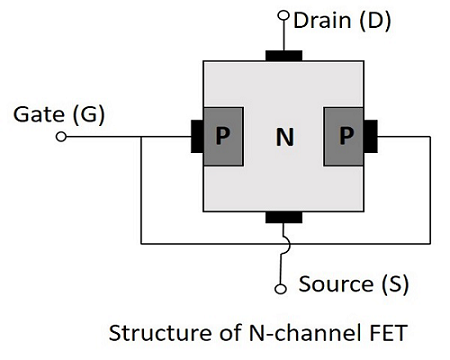

这两个栅极沉积物(P型材料)形成两个PN结二极管。栅极之间的区域称为沟道。多数载流子通过该沟道。因此,FET的横截面形式如下图所示。

在N型半导体棒的两端形成欧姆接触,形成源极和漏极。源极和漏极端子可以互换。

N沟道FET的工作原理

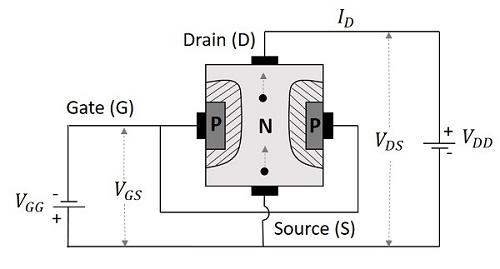

在了解FET的工作原理之前,应该了解耗尽层的形成方式。为此,让我们假设栅极端子的电压,例如VGG,是反向偏置的,而漏极端子的电压,例如VDD,则未施加。设此为情况1。

在情况1中,当VGG反向偏置且VDD未施加时,P层和N层之间的耗尽区会扩展。这是因为施加的负电压会将空穴从P型层吸引到栅极端子。

在情况2中,当施加VDD(正极连接到漏极,负极连接到源极)且VGG未施加时,电子从源极流向漏极,构成漏极电流ID。

现在让我们考虑下图,以了解同时施加两个电源时会发生什么。

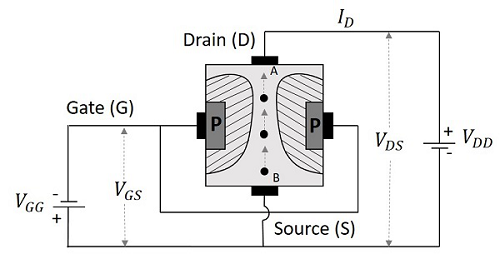

栅极端子的电源使耗尽层增大,漏极端子的电压允许漏极电流从源极流向漏极端子。假设源极端子的点为B,漏极端子的点为A,则沟道的电阻将使得A端子的电压降大于B端子的电压降。这意味着:

VA>VB

因此,电压降沿沟道长度逐渐增大。因此,反向偏置效应在漏极端子比在源极端子更强。这就是为什么当同时施加VGG和VDD时,耗尽层倾向于在A点比在B点更深入地渗透到沟道中。下图说明了这一点。

现在我们已经了解了FET的行为,让我们了解FET的实际工作原理。

耗尽型工作模式

由于耗尽层的宽度在FET的工作中起着重要作用,因此称为耗尽型工作模式。我们还有另一种称为增强型工作模式,这将在MOSFET的工作原理中讨论。但JFET只有耗尽型工作模式。

让我们考虑一下栅极和源极端子之间没有施加电位,并且在漏极和源极之间施加了电位VDD。现在,电流ID从漏极流向源极端子,因为沟道宽度较大,所以电流达到最大值。设栅极和源极端子之间施加的电压VGG为反向偏置。这会增加耗尽层的宽度,如上所述。随着层增厚,沟道的横截面积减小,因此漏极电流ID也减小。

当进一步增加该漏极电流时,会发生一个阶段,其中两个耗尽层相互接触,并阻止电流ID流动。下图清楚地显示了这一点。

这两个耗尽层实际上“接触”的电压称为“夹断电压”。它表示为VP。此时漏极电流实际上为零。因此,漏极电流是栅极反向偏置电压的函数。

由于栅极电压控制漏极电流,因此FET被称为电压控制型器件。这从漏极特性曲线可以更清楚地理解。

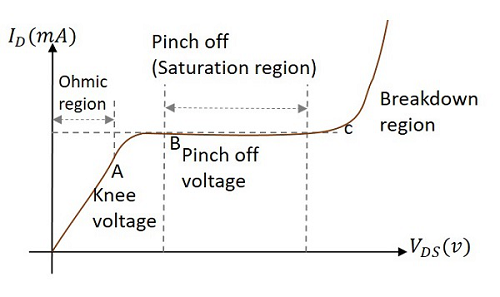

JFET的漏极特性

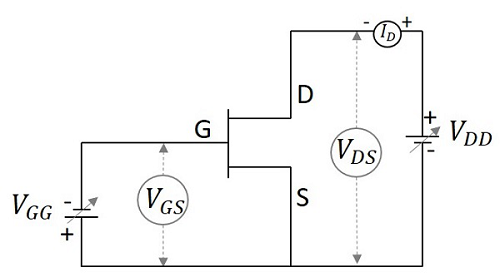

让我们尝试总结FET的功能,通过该功能我们可以获得FET漏极的特性曲线。下面给出用于获得这些特性的FET电路。

当栅极和源极之间的电压VGS为零或它们短路时,从源极到漏极的电流ID也为零,因为没有施加VDS。随着漏极和源极之间电压VDS的增加,从源极到漏极的电流流ID增加。电流的增加在某个点A(称为膝电压)之前是线性的。

栅极端子将处于反向偏置状态,并且随着ID的增加,耗尽区趋于收缩。这种收缩的长度不相等,使得这些区域在漏极处靠近,在源极处远离,这会导致夹断电压。夹断电压定义为漏极电流接近恒定值(饱和值)时的最小漏极到源极电压。发生此夹断电压的点称为夹断点,表示为B。

随着VDS的进一步增加,沟道电阻也相应增加,以至于ID实际上保持恒定。区域BC称为饱和区或放大器区。所有这些以及点A、B和C都绘制在下图中。

对于不同的栅极源极电压VGS值,绘制漏极电流ID对漏极源极电压VDS的漏极特性曲线。对于各种输入电压,总体漏极特性如下所示。

由于负栅极电压控制漏极电流,因此FET被称为电压控制型器件。漏极特性表示FET的性能。上面绘制的漏极特性用于获得漏极电阻、跨导和放大系数的值。