- 超大规模集成电路设计教程

- 超大规模集成电路设计 - 首页

- 超大规模集成电路设计 - 数字系统

- 超大规模集成电路设计 - FPGA技术

- 超大规模集成电路设计 - MOS晶体管

- 超大规模集成电路设计 - MOS反相器

- 组合MOS逻辑电路

- 时序MOS逻辑电路

- VHDL编程

- VHDL - 简介

- VHDL - 组合电路

- VHDL - 时序电路

- Verilog

- Verilog - 简介

- 行为建模与时序

- 超大规模集成电路设计有用资源

- 超大规模集成电路设计 - 快速指南

- 超大规模集成电路设计 - 有用资源

- 超大规模集成电路设计 - 讨论

超大规模集成电路设计 - MOS反相器

反相器确实是所有数字设计的核心。一旦清楚地理解了它的工作原理和特性,设计更复杂的结构,如与非门、加法器、乘法器和微处理器,就会大大简化。这些复杂电路的电气行为几乎可以完全通过外推反相器的结果来推导。

反相器的分析可以扩展到解释更复杂门(如与非门、或非门或异或门)的行为,而这些门反过来又构成乘法器和处理器等模块的构建块。在本章中,我们将重点关注反相器门的单一实现形式,即静态CMOS反相器——简称CMOS反相器。这当然是目前最流行的,因此值得我们特别关注。

工作原理

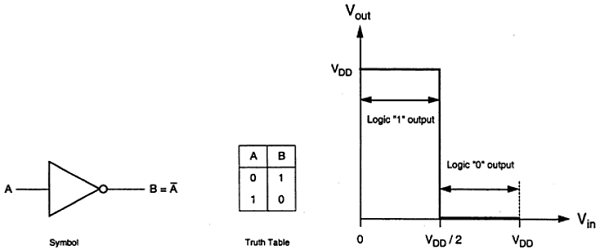

理想反相器的逻辑符号和真值表如下所示。这里A是输入,B是反相输出,由它们的节点电压表示。使用正逻辑,逻辑1的布尔值由Vdd表示,逻辑0由0表示。Vth是反相器阈值电压,等于Vdd /2,其中Vdd是输出电压。

当输入小于Vth时,输出从0切换到Vdd。因此,对于0<Vin<Vth,输出等于逻辑0输入;对于Vth<Vin< Vdd,输出等于反相器的逻辑1输入。

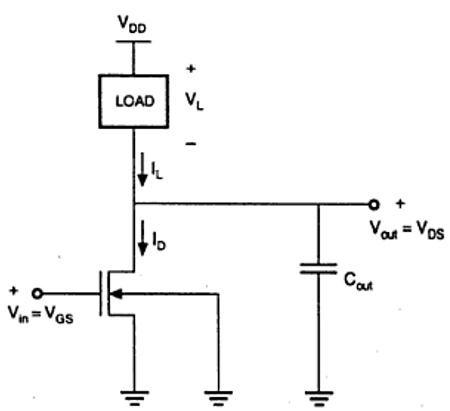

图中所示的特性是理想的。nMOS反相器的通用电路结构如下图所示。

从上图可以看出,反相器的输入电压等于nMOS晶体管的栅源电压,反相器的输出电压等于nMOS晶体管的漏源电压。nMOS的源衬电压也称为晶体管的驱动器,其接地;因此VSS = 0。输出节点连接到用于VTC的集总电容。

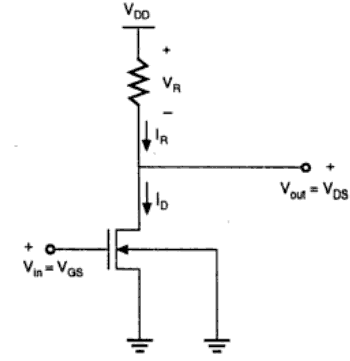

电阻负载反相器

电阻负载反相器的基本结构如下图所示。这里,增强型nMOS充当驱动晶体管。负载由一个简单的线性电阻RL组成。电路的电源是VDD,漏极电流ID等于负载电流IR。

电路工作

当驱动晶体管的输入小于阈值电压VTH (Vin < VTH)时,驱动晶体管处于截止区域,不导通任何电流。因此,负载电阻上的电压降为零,输出电压等于VDD。现在,当输入电压进一步增加时,驱动晶体管将开始导通非零电流,nMOS进入饱和区。

数学上,

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

进一步增加输入电压,驱动晶体管将进入线性区,驱动晶体管的输出减小。

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

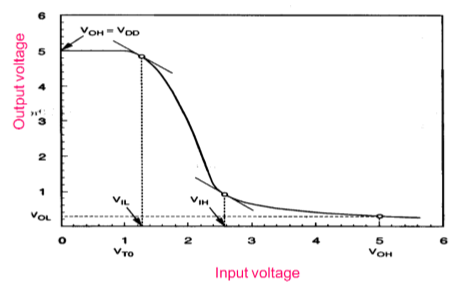

下图所示的电阻负载反相器的VTC指示驱动晶体管的工作模式和电压点。

带N型MOSFET负载的反相器

使用MOSFET作为负载器件的主要优点是晶体管占用的硅面积小于电阻负载占用的面积。这里,MOSFET是有源负载,具有有源负载的反相器比具有电阻负载的反相器具有更好的性能。

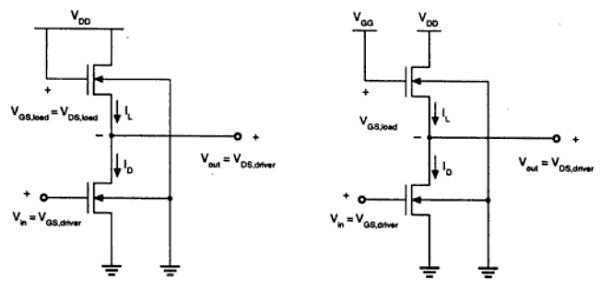

增强型负载NMOS

图中显示了两个具有增强型负载器件的反相器。负载晶体管可以在饱和区或线性区工作,这取决于施加到其栅极端的偏置电压。饱和增强型负载反相器如图(a)所示。它只需要单电源和简单的制造工艺,因此VOH 限制在VDD − VT。

线性增强型负载反相器如图(b)所示。它始终在线性区工作;因此VOH 电平等于VDD。

与饱和增强型反相器相比,线性负载反相器具有更高的噪声容限。但是,线性增强型反相器的缺点是它需要两个独立的电源,并且这两个电路都存在功耗高的缺点。因此,增强型反相器不用于任何大规模数字应用。

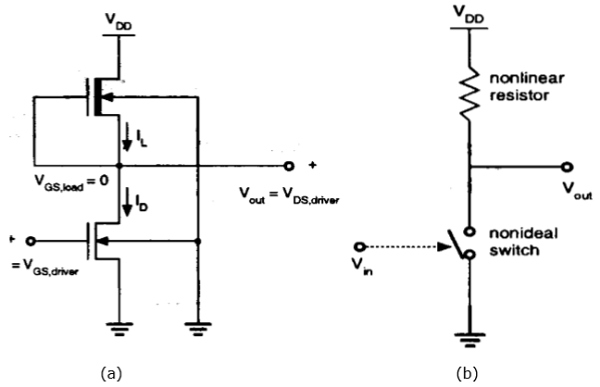

耗尽型负载NMOS

增强型负载反相器的缺点可以通过使用耗尽型负载反相器来克服。与增强型负载反相器相比,耗尽型负载反相器需要更多的制造步骤来进行沟道注入以调整负载的阈值电压。

耗尽型负载反相器的优点是:VTC转换尖锐、噪声容限更好、单电源和更小的整体布局面积。

如图所示,负载的栅极和源极端子相连;因此,VGS = 0。因此,负载的阈值电压为负。因此,

$$V_{GS,load}> V_{T,load}$$ 成立

因此,无论输入和输出电压电平如何,负载器件始终具有导电通道。

当负载晶体管处于饱和区时,负载电流由下式给出

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ -V_{T,load}\left ( V_{out} \right ) \right ]^{2}$$

当负载晶体管处于线性区时,负载电流由下式给出

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \right ]$$

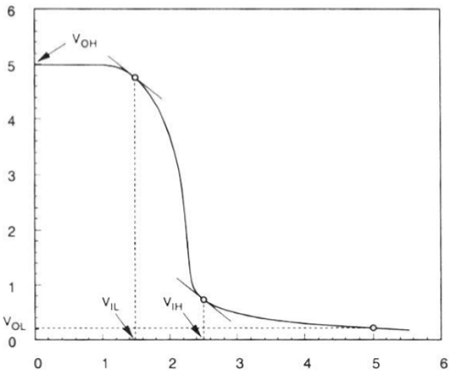

耗尽型负载反相器的电压传输特性如下图所示:

CMOS反相器 – 电路、工作原理和描述

CMOS反相器电路如下图所示。这里,nMOS和pMOS晶体管充当驱动晶体管;当一个晶体管导通时,另一个晶体管截止。

这种配置称为互补MOS (CMOS)。输入连接到两个晶体管的栅极端子,以便可以直接用输入电压驱动两者。nMOS的衬底连接到地,pMOS的衬底连接到电源VDD。

因此,两个晶体管的VSB = 0。

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{out}$$

而且,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

当nMOS的输入小于阈值电压(Vin < VTO,n)时,nMOS截止,pMOS处于线性区。因此,两个晶体管的漏极电流都为零。

$$I_{D,n}=I_{D,p}=0$$

因此,输出电压VOH等于电源电压。

$$V_{out}=V_{OH}=V_{DD}$$

当输入电压大于VDD + VTO,p时,pMOS晶体管处于截止区,nMOS处于线性区,因此两个晶体管的漏极电流都为零。

$$I_{D,n}=I_{D,p}=0$$

因此,输出电压VOL等于零。

$$V_{out}=V_{OL}=0$$

如果Vin > VTO并且满足以下条件,则nMOS工作在饱和区。

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{out}\geq V_{in}-V_{TO,n} $$

如果Vin < VDD + VTO,p并且满足以下条件,则pMOS工作在饱和区。

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{out}\leq V_{in}-V_{TO,p} $$

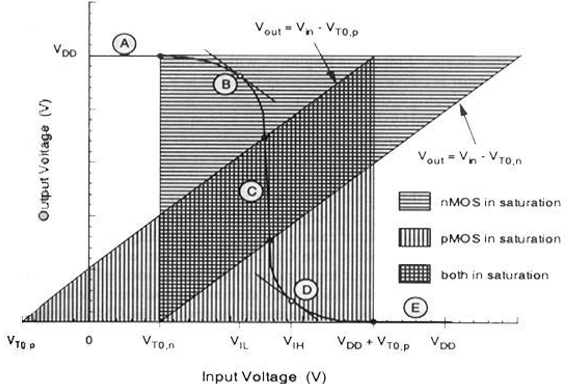

对于不同的输入电压值,下面列出了两个晶体管的工作区域。

| 区域 | Vin | Vout | nMOS | pMOS |

|---|---|---|---|---|

| A | < VTO, n | VOH | 截止 | 线性 |

| B | VIL | 高 ≈ VOH | 饱和 | 线性 |

| C | Vth | Vth | 饱和 | 饱和 |

| D | VIH | 低 ≈ VOL | 线性 | 饱和 |

| E | > (VDD + VTO, p) | VOL | 线性 | 截止 |

CMOS的VTC如下图所示: