- 超大规模集成电路设计教程

- 超大规模集成电路设计 - 首页

- 超大规模集成电路设计 - 数字系统

- 超大规模集成电路设计 - FPGA技术

- 超大规模集成电路设计 - MOS晶体管

- 超大规模集成电路设计 - MOS反相器

- 组合MOS逻辑电路

- 时序MOS逻辑电路

- VHDL编程

- VHDL - 简介

- VHDL - 组合电路

- VHDL - 时序电路

- Verilog

- Verilog - 简介

- 行为建模与时序

- 超大规模集成电路设计实用资源

- 超大规模集成电路设计 - 快速指南

- 超大规模集成电路设计 - 有用资源

- 超大规模集成电路设计 - 讨论

超大规模集成电路设计 - MOS晶体管

互补金属氧化物半导体(CMOS)技术现已被广泛用于在众多不同应用中形成电路。如今的计算机、CPU和手机都利用CMOS,因为它具有若干关键优势。CMOS具有低功耗、相对较高的速度、两种状态下均具有较高的噪声容限,并且可以在较宽的电源和输入电压范围内工作(前提是电源电压固定)。

对于我们将讨论的过程,可用的晶体管类型是金属氧化物半导体场效应晶体管(MOSFET)。这些晶体管像“三明治”一样形成,由半导体层(通常是切片或晶圆,来自单晶硅)、一层二氧化硅(氧化物)和一层金属组成。

MOSFET的结构

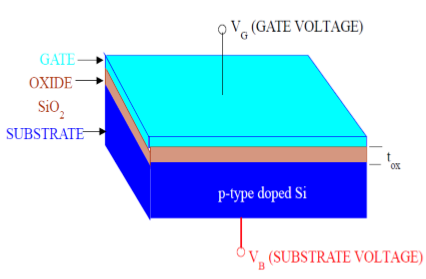

如图所示,MOS结构包含三层:

金属栅极电极

绝缘氧化物层(SiO2)

P型半导体(衬底)

MOS结构形成一个电容器,其中栅极和衬底作为两个极板,氧化物层作为介电材料。介电材料(SiO2)的厚度通常在10 nm到50 nm之间。可以通过施加到栅极和衬底端子的外部电压来控制衬底内的载流子浓度和分布。现在,为了理解MOS结构,首先考虑P型半导体衬底的基本电学特性。

半导体材料中载流子的浓度始终遵循质量作用定律。质量作用定律表示为:

$$n.p=n_{i}^{2}$$

其中,

n是电子载流子浓度

p是空穴载流子浓度

ni是硅的本征载流子浓度

现在假设衬底均匀掺杂了受主(硼)浓度NA。因此,p型衬底中的电子和空穴浓度为

$$n_{po}=\frac{n_{i}^{2}}{N_{A}}$$

$$p_{po}=N_{A}$$

这里,掺杂浓度NA比本征浓度ni大(1015到1016 cm−3)。现在,为了理解MOS结构,请考虑p型硅衬底的能级图。

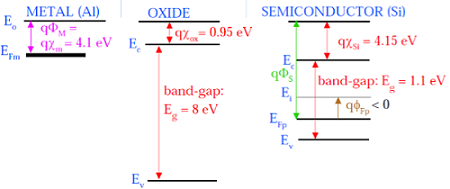

如图所示,导带和价带之间的带隙为1.1eV。这里,费米势ΦF是本征费米能级(Ei)和费米能级(EFP)之间的差值。

其中费米能级EF取决于掺杂浓度。费米势ΦF是本征费米能级(Ei)和费米能级(EFP)之间的差值。

数学上表示为:

$$\Phi_{Fp}=\frac{E_{F}-E_{i}}{q}$$

导带和自由空间之间的电势差称为电子亲和势,用qx表示。

因此,电子从费米能级移动到自由空间所需的能量称为功函数(qΦS),其表示为

$$q\Phi _{s}=(E_{c}-E_{F})+qx$$

下图显示了构成MOS的组件的能带图。

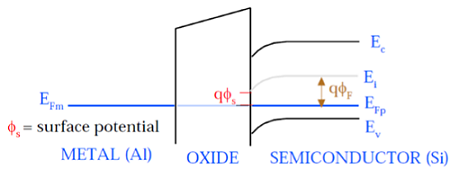

如上图所示,绝缘SiO2层具有8eV的大能带隙,功函数为0.95 eV。金属栅极的功函数为4.1eV。这里,功函数不同,因此会在MOS系统上产生电压降。下图显示了MOS系统的组合能带图。

如图所示,金属栅极和半导体(Si)的费米势能级处于相同电势。表面处的费米势称为表面势ΦS,其大小小于费米势ΦF。

MOSFET的工作原理

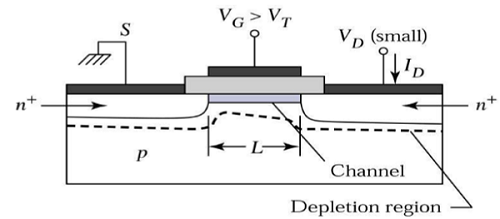

MOSFET由一个MOS电容器组成,该电容器有两个p-n结放置在靠近沟道区域,并且该区域受栅极电压控制。为了使两个p-n结反向偏置,衬底电势保持低于其他三个端子的电势。

如果栅极电压超过阈值电压(VGS>VTO),则会在表面上建立反型层,并且将在源极和漏极之间形成n型沟道。此n型沟道将根据VDS值承载漏极电流。

对于VDS的不同值,MOSFET可以在不同区域工作,如下所述。

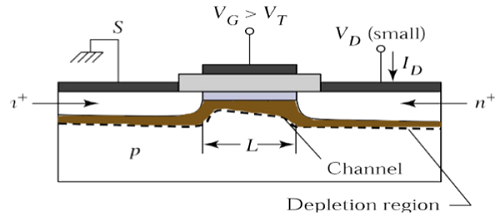

线性区域

在VDS = 0时,反型沟道区域存在热平衡,漏极电流ID = 0。现在,如果施加小的漏极电压VDS > 0,则与VDS成正比的漏极电流将开始从源极流向漏极穿过沟道。

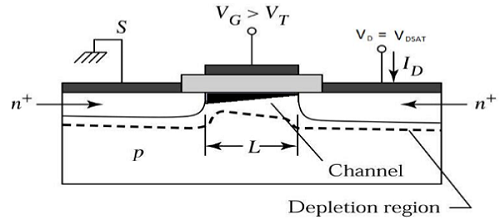

沟道为电流从源极流向漏极提供了连续路径。这种工作模式称为线性区域。下图显示了在线性区域工作时n沟道MOSFET的横截面视图。

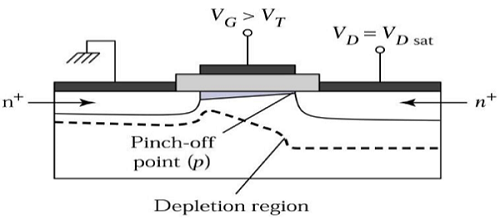

饱和区域边缘

现在,如果增加VDS,则沟道中的电荷和沟道深度在漏极端部减小。对于VDS = VDSAT,沟道中的电荷减小到零,这称为夹断点。下图显示了在饱和区域边缘工作的n沟道MOSFET的横截面视图。

饱和区域

对于VDS>VDSAT,在漏极附近会形成耗尽表面,并且通过增加漏极电压,该耗尽区域扩展到源极。

这种工作模式称为饱和区域。来自源极进入沟道末端的电子进入漏极耗尽区域,并在高电场中加速向漏极移动。

MOSFET电流-电压特性

为了理解MOSFET的电流-电压特性,对沟道进行了近似。如果没有此近似值,MOS系统的三维分析将变得复杂。用于电流-电压特性的渐变沟道近似(GCA)将简化分析问题。

渐变沟道近似(GCA)

考虑在线性模式下工作的n沟道MOSFET的横截面视图。这里,源极和衬底连接到地。VS = VB = 0。栅极到源极(VGS)和漏极到源极电压(VDS)电压是控制漏极电流ID的外部参数。

VGS电压设置为大于阈值电压VTO的电压,以在源极和漏极之间创建沟道。如图所示,x方向垂直于表面,y方向平行于表面。

这里,y = 0位于源极端部,如图所示。相对于源极的沟道电压用VC(Y)表示。假设阈值电压VTO在源极到漏极之间的沟道区域内是恒定的。沟道电压VC的边界条件为:

$$V_{c}\left ( y = 0 \right ) = V_{s} = 0 \,and\,V_{c}\left ( y = L \right ) = V_{DS}$$

我们还可以假设

$$V_{GS}\geq V_{TO}$$ 并且

$$V_{GD} = V_{GS}-V_{DS}\geq V_{TO}$$

令Q1(y)为表面反型层中的总移动电子电荷。此电子电荷可以表示为:

$$Q1(y)=-C_{ox}.[V_{GS}-V_{C(Y)}-V_{TO}]$$

下图显示了表面反型层的空间几何形状并指示其尺寸。当我们从漏极移动到源极时,反型层逐渐消失。现在,如果我们考虑沟道长度L的小区域dy,则此区域提供的增量电阻dR可以表示为:

$$dR=-\frac{dy}{w.\mu _{n}.Q1(y)}$$

这里,负号是由于反型层电荷Q1的负极性,μn是表面迁移率,是常数。现在,将Q1(y)的值代入dR方程:

$$dR=-\frac{dy}{w.\mu _{n}.\left \{ -C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO} \right \}}$$

$$dR=\frac{dy}{w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO}}$$

现在,小区域dy中的电压降可以表示为

$$dV_{c}=I_{D}.dR$$

将dR的值代入上述方程

$$dV_{C}=I_{D}.\frac{dy}{w.\mu_{n}.C_{ox}\left [ V_{GS}-V_{C(Y)} \right ]-V_{TO}}$$

$$w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C(Y)}-V_{TO} \right ].dV_{C}=I_{D}.dy$$

为了获得整个沟道区域上的漏极电流ID,上述方程可以在沟道沿y = 0到y = L积分,电压VC(y) = 0到VC(y) = VDS,

$$C_{ox}.w.\mu _{n}.\int_{V_{c}=0}^{V_{DS}} \left [ V_{GS}-V_{C\left ( Y \right )}-V_{TO} \right ].dV_{C} = \int_{Y=0}^{L}I_{D}.dy$$

$$\frac{C_{ox}.w.\mu _{n}}{2}\left ( 2\left [ V_{GS}-V_{TO} \right ] V_{DS}-V_{DS}^{2}\right ) = I_{D}\left [ L-0 \right ]$$

$$I_{D} = \frac{C_{ox}.\mu _{n}}{2}.\frac{w}{L}\left ( 2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2} \right )$$

对于线性区域VDS < VGS − VTO。对于饱和区域,VDS的值大于(VGS − VTO)。因此,对于饱和区域VDS = (VGS − VTO)。

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ 2V_{DS} \right ]V_{DS}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{2V_{DS}^{2}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ V_{GS}-V_{TO} \right ]^{2}}{L} \right )$$