- 数字电子教程

- 数字电子 - 首页

- 数字电子基础

- 数字系统类型

- 信号类型

- 逻辑电平和脉冲波形

- 数字系统组件

- 数字逻辑运算

- 数字系统优势

- 进制系统

- 进制系统

- 二进制数表示

- 二进制运算

- 有符号二进制运算

- 八进制运算

- 十六进制运算

- 补码运算

- 进制转换

- 进制转换

- 二进制转十进制

- 十进制转二进制

- 二进制转八进制

- 八进制转二进制

- 八进制转十进制

- 十进制转八进制

- 十六进制转二进制

- 二进制转十六进制

- 十六进制转十进制

- 十进制转十六进制

- 八进制转十六进制

- 十六进制转八进制

- 二进制编码

- 二进制编码

- 8421 BCD码

- 余3码

- 格雷码

- ASCII码

- EBCDIC码

- 代码转换

- 检错纠错码

- 逻辑门

- 逻辑门

- 与门

- 或门

- 非门

- 通用门

- 异或门

- 异或非门

- CMOS逻辑门

- 用二极管电阻逻辑实现的或门

- 与门与或门的比较

- 二层逻辑实现

- 阈值逻辑

- 布尔代数

- 布尔代数

- 布尔代数定律

- 布尔函数

- 德摩根定理

- SOP和POS形式

- POS到标准POS形式

- 最小化技术

- 卡诺图化简

- 三变量卡诺图

- 四变量卡诺图

- 五变量卡诺图

- 六变量卡诺图

- 无关项条件

- 奎因-麦克拉斯基法

- 最小项和最大项

- 规范式和标准式

- 最大项表示

- 使用布尔代数化简

- 组合逻辑电路

- 数字组合电路

- 数字运算电路

- 多路选择器

- 多路选择器设计步骤

- 多路选择器通用门

- 使用4:1多路选择器的2变量函数

- 使用8:1多路选择器的3变量函数

- 多路分配器

- 多路选择器与多路分配器的比较

- 奇偶校验位发生器和校验器

- 比较器

- 编码器

- 键盘编码器

- 优先编码器

- 译码器

- 算术逻辑单元

- 7段LED显示器

- 代码转换器

- 代码转换器

- 二进制转十进制转换器

- 十进制转BCD转换器

- BCD转十进制转换器

- 二进制转格雷码转换器

- 格雷码转二进制转换器

- BCD转余3码转换器

- 余3码转BCD转换器

- 加法器

- 半加器

- 全加器

- 串行加法器

- 并行加法器

- 使用半加器实现的全加器

- 半加器与全加器的比较

- 使用NAND门的全加器

- 使用NAND门的半加器

- 二进制加减法器

- 减法器

- 半减器

- 全减器

- 并行减法器

- 使用两个半减器实现的全减器

- 使用NAND门的半减器

- 时序逻辑电路

- 数字时序电路

- 时钟信号和触发

- 锁存器

- 移位寄存器

- 移位寄存器应用

- 二进制寄存器

- 双向移位寄存器

- 计数器

- 二进制计数器

- 非二进制计数器

- 同步计数器设计

- 同步计数器与异步计数器的比较

- 有限状态机

- 算法状态机

- 触发器

- 触发器

- 触发器转换

- D触发器

- JK触发器

- T触发器

- SR触发器

- 带时钟的SR触发器

- 无时钟SR触发器

- 带时钟的JK触发器

- JK触发器转T触发器

- SR触发器转JK触发器

- 触发方式:触发器

- 边沿触发触发器

- 主从JK触发器

- 竞争冒险现象

- A/D和D/A转换器

- 模数转换器

- 数模转换器

- 数模转换器和模数转换器IC

- 逻辑门的实现

- 用NAND门实现非门

- 用NAND门实现或门

- 用NAND门实现与门

- 用NAND门实现或非门

- 用NAND门实现异或门

- 用NAND门实现异或非门

- 用NOR门实现非门

- 用NOR门实现或门

- 用NOR门实现与门

- 用NOR门实现与非门

- 用NOR门实现异或门

- 用NOR门实现异或非门

- 使用CMOS的与非/或非门

- 使用NAND门实现的全减器

- 使用2:1多路选择器的与门

- 使用2:1多路选择器的或门

- 使用2:1多路选择器的非门

- 存储器件

- 存储器件

- RAM和ROM

- 高速缓存设计

- 可编程逻辑器件

- 可编程逻辑器件

- 可编程逻辑阵列

- 可编程阵列逻辑

- 现场可编程门阵列

- 数字电子系列

- 数字电子系列

- CPU 架构

- CPU 架构

- 数字电子资源

- 数字电子 - 快速指南

- 数字电子 - 资源

- 数字电子 - 讨论

CPU 架构

微处理器与传统计算机中使用的中央处理器 (CPU) 同义。微处理器 (MPU) 充当执行以下任务的设备或设备组。

- 与外围设备通信

- 提供定时信号

- 直接数据流

- 根据内存中的指令执行计算机任务

8085 微处理器

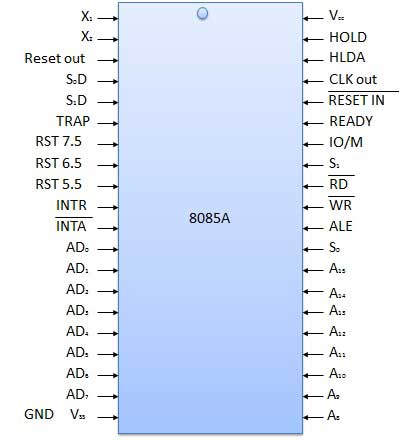

8085 微处理器是一个 8 位通用微处理器,能够寻址 64k 的内存。该处理器有 40 个引脚,需要 +5 V 单电源和 3 MHz 单相时钟。

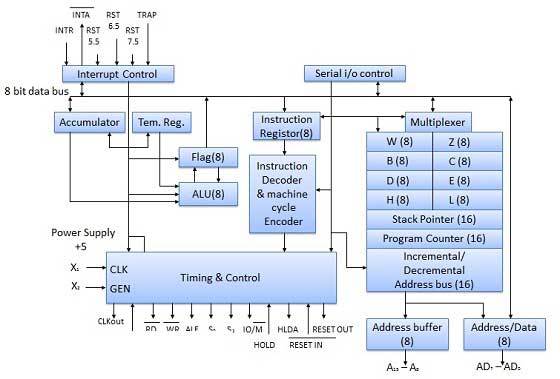

框图

算术逻辑单元 (ALU)

ALU 执行微处理器的计算功能。它包括累加器、临时寄存器、算术和逻辑电路以及五个标志。结果存储在累加器和标志中。

框图

累加器

它是一个 8 位寄存器,是 ALU 的一部分。该寄存器用于存储 8 位数据并在执行算术和逻辑运算时使用。运算结果存储在累加器中。

图表

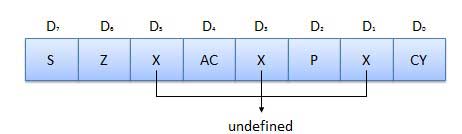

标志

标志是可编程的。它们可用于通过指令存储和传输来自寄存器的数据。ALU 包含五个触发器,根据累加器和其他寄存器中的数据条件进行设置和复位。

- S(符号)标志 - 算术运算执行后,如果结果的位 D7 为 1,则设置符号标志。它用于有符号数。在给定的字节中,如果 D7 为 1,则表示负数。如果为零,则表示正数。

- Z(零)标志 - 如果 ALU 运算结果为 0,则设置零标志。

- AC(辅助进位)标志 - 在算术运算中,当由数字 D3 生成进位并传递到数字 D4 时,设置 AC 标志。此标志仅在内部 BCD 运算中使用。

- P(奇偶校验)标志 - 算术或逻辑运算后,如果结果中 1 的个数为偶数,则设置标志。如果 1 的个数为奇数,则复位标志。

- C(进位)标志 - 如果算术运算结果有进位,则设置进位标志,否则复位。

寄存器部分

它基本上是一个存储设备,并通过使用指令传输来自寄存器的数据。

- 堆栈指针 (SP) - 堆栈指针也是一个 16 位寄存器,用作内存指针。它指向读/写内存中称为堆栈的内存位置。在程序执行期间,有时需要将数据存储到堆栈中。堆栈的起始位置是通过在堆栈指针中加载一个 16 位地址来定义的。

- 程序计数器 (PC) - 此 16 位寄存器处理第四个操作以顺序执行指令。此寄存器也是内存指针。内存位置具有 16 位地址。它用于存储执行地址。程序计数器的功能是从要从中提取下一个字节的内存地址指向。

- 存储寄存器 - 这些寄存器在程序执行期间存储 8 位数据。这些寄存器被标识为 B、C、D、E、H、L。它们可以组合成寄存器对 BC、DE 和 HL 以执行某些 16 位操作。

时间和控制部分

此单元负责根据时钟脉冲同步微处理器操作,并生成微处理器与外围设备之间平滑通信所需的控制信号。RD 信号和 WR 信号是同步脉冲,指示数据是否在数据总线上可用。控制单元负责控制微处理器、内存和外围设备之间的数据流。

引脚图

所有信号可分为六组

| 序号 | 组 | 描述 |

|---|---|---|

| 1 | 地址总线 | 8085 微处理器有 8 条信号线 A15 - A8,它们是单向的,用作高位地址总线。 |

| 2 | 数据总线 | 信号线 AD7 - AD0 是双向的,用于双重用途。它们用作低位地址总线以及数据总线。 |

| 3 | 控制信号和状态信号 |

控制信号 RD 信号 - 这是一个读控制信号(低电平有效)。如果它处于活动状态,则内存读取数据。 WR 信号 - 这是一个写控制信号(低电平有效)。写入选定的内存时,它处于活动状态。 状态信号 ALE(地址锁存使能) - 当 ALE 为高电平时,8085 微处理器使用地址总线。当 ALE 为低电平时,8085 微处理器使用数据总线。 IO/M 信号 - 这是一个状态信号,用于区分 I/O 和内存操作。当它为高电平时,表示 I/O 操作;当它为低电平时,表示内存操作。 S1 和 S0 - 这些状态信号类似于 I/O 和内存信号,可以识别各种操作,但在小型系统中很少使用。 |

| 4 | 电源和频率信号 |

Vcc - +5v 电源。 Vss - 接地参考。 X1, X2 - 晶体连接在这两个引脚上。频率在内部除以二,以 3 MHz 运行系统,晶体的频率应为 6 MHz。 CLK out - 此信号可用作其他设备的系统时钟。 |

| 5 | 外部启动信号 |

INTR(输入) - 中断请求。 INTA 信号(输出) - 它用作中断应答。 TRAP(输入) - 这是一个不可屏蔽中断,具有最高优先级。 HOLD(输入) - 用于暂停正在执行的程序。 HLDA(输出) - 保持应答。 READY(输入) - 此信号用于延迟微处理器读或写周期,直到响应缓慢的外围设备准备好接收或发送数据。 RESET IN 信号 - 当此引脚上的信号变低时,程序计数器设置为零,总线变为高阻态,MPU 复位。 RESET OUT - 此信号指示 MPU 正在复位。该信号可用于复位其他设备。 RST 7.5、RST 6.5、RST 5.5(请求中断)− 用于将程序控制转移到特定的内存位置。它们的优先级高于INTR中断。 |

| 6 | 串行I/O端口 | 8085微处理器有两个信号来实现串行传输:串行输入数据和串行输出数据。 |

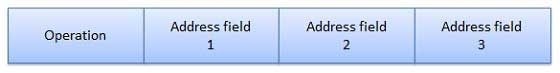

指令格式

每条指令都由计算机内部的一系列位表示。指令被分成称为字段的位组。指令的表达方式称为指令格式。它通常以矩形框的形式表示。指令格式可以是以下类型。

变长指令格式

这些指令格式的指令长度根据操作码和地址说明符而变化。例如,VAX指令的长度在1到53字节之间变化,而X86指令的长度在1到17字节之间变化。

格式

优点

这些格式具有良好的代码密度。

缺点

这些指令格式很难解码和流水线化。

定长指令格式

在这种类型的指令格式中,所有指令的大小都相同。例如,MIPS、Power PC、Alpha、ARM。

格式

优点

它们易于解码和流水线化。

缺点

它们的代码密度不高。

混合指令格式

在这种类型的指令格式中,我们有多种由操作码指定的格式长度。例如,IBM 360/70、MIPS 16、Thumb。

格式

优点

这些格式在代码密度和指令解码容易性之间进行了折衷。

寻址方式

寻址方式为处理器访问给定数据的地址提供了不同的方法。操作数据存储在内存位置中,每条指令都需要某些数据来进行操作。有各种技术可以指定数据的地址。这些技术称为寻址方式。

- 直接寻址方式− 在直接寻址方式中,操作数的地址在指令中给出,数据位于指令中提供的内存位置。我们将把这个数据移动到所需的位置。

- 间接寻址方式− 在间接寻址方式中,指令指定一个寄存器,该寄存器包含操作数的地址。内部RAM和外部RAM都可以通过间接寻址方式访问。

- 立即寻址方式− 在立即寻址方式中,直接数据在操作数中给出,并将数据移入累加器。它非常快。

- 相对寻址方式− 在相对寻址方式中,有效地址由索引模式使用程序计数器而不是通用处理器寄存器来确定。这种模式称为相对寻址方式。

- 索引寻址方式− 在索引寻址方式中,操作数的有效地址是通过将内容值添加到寄存器的内容生成的。这种模式称为索引寻址方式。