- 数字电子教程

- 数字电子 - 首页

- 数字电子基础

- 数字系统的类型

- 信号的类型

- 逻辑电平和脉冲波形

- 数字系统组件

- 数字逻辑运算

- 数字系统优势

- 数制

- 数制

- 二进制数的表示

- 二进制运算

- 带符号二进制运算

- 八进制运算

- 十六进制运算

- 补码运算

- 进制转换

- 进制转换

- 二进制到十进制转换

- 十进制到二进制转换

- 二进制到八进制转换

- 八进制到二进制转换

- 八进制到十进制转换

- 十进制到八进制转换

- 十六进制到二进制转换

- 二进制到十六进制转换

- 十六进制到十进制转换

- 十进制到十六进制转换

- 八进制到十六进制转换

- 十六进制到八进制转换

- 二进制编码

- 二进制编码

- 8421 BCD码

- 余3码

- 格雷码

- ASCII码

- EBCDIC码

- 代码转换

- 错误检测与纠错码

- 逻辑门

- 逻辑门

- 与门

- 或门

- 非门

- 通用门

- 异或门

- 异或非门

- CMOS逻辑门

- 使用二极管电阻逻辑的或门

- 与门与或门

- 双电平逻辑实现

- 阈值逻辑

- 布尔代数

- 布尔代数

- 布尔代数定律

- 布尔函数

- 德摩根定理

- SOP和POS形式

- POS到标准POS形式

- 最小化技术

- 卡诺图最小化

- 三变量卡诺图

- 四变量卡诺图

- 五变量卡诺图

- 六变量卡诺图

- 无关项条件

- 奎因-麦克拉斯基方法

- 最小项和最大项

- 规范式和标准式

- 最大项表示

- 使用布尔代数化简

- 组合逻辑电路

- 数字组合电路

- 数字算术电路

- 多路复用器

- 多路复用器设计流程

- MUX通用门

- 使用4:1MUX的2变量函数

- 使用8:1MUX的3变量函数

- 多路分解器

- MUX与DEMUX

- 奇偶校验位生成器和校验器

- 比较器

- 编码器

- 键盘编码器

- 优先编码器

- 译码器

- 算术逻辑单元

- 7段LED显示器

- 代码转换器

- 代码转换器

- 二进制到十进制转换器

- 十进制到BCD转换器

- BCD到十进制转换器

- 二进制到格雷码转换器

- 格雷码到二进制转换器

- BCD到余3码转换器

- 余3码到BCD转换器

- 加法器

- 半加器

- 全加器

- 串行加法器

- 并行加法器

- 使用半加器的全加器

- 半加器与全加器

- 使用与非门的全加器

- 使用与非门的半加器

- 二进制加法/减法器

- 减法器

- 半减器

- 全减器

- 并行减法器

- 使用2个半减器的全减器

- 使用与非门的半减器

- 时序逻辑电路

- 数字时序电路

- 时钟信号和触发

- 锁存器

- 移位寄存器

- 移位寄存器应用

- 二进制寄存器

- 双向移位寄存器

- 计数器

- 二进制计数器

- 非二进制计数器

- 同步计数器设计

- 同步计数器与异步计数器

- 有限状态机

- 算法状态机

- 触发器

- 触发器

- 触发器转换

- D触发器

- JK触发器

- T触发器

- SR触发器

- 带时钟的SR触发器

- 无时钟的SR触发器

- 带时钟的JK触发器

- JK到T触发器

- SR到JK触发器

- 触发方法:触发器

- 边沿触发触发器

- 主从JK触发器

- 竞争冒险现象

- A/D和D/A转换器

- 模数转换器

- 数模转换器

- DAC和ADC集成电路

- 逻辑门的实现

- 用与非门实现非门

- 用与非门实现或门

- 用与非门实现与门

- 用与非门实现或非门

- 用与非门实现异或门

- 用与非门实现异或非门

- 用或非门实现非门

- 用或非门实现或门

- 用或非门实现与门

- 用或非门实现与非门

- 用或非门实现异或门

- 用或非门实现异或非门

- 使用CMOS的与非/或非门

- 使用与非门的全减器

- 使用2:1MUX的与门

- 使用2:1MUX的或门

- 使用2:1MUX的非门

- 存储器件

- 存储器件

- RAM和ROM

- 高速缓存存储器设计

- 可编程逻辑器件

- 可编程逻辑器件

- 可编程逻辑阵列

- 可编程阵列逻辑

- 现场可编程门阵列

- 数字电子系列

- 数字电子系列

- CPU架构

- CPU架构

- 数字电子资源

- 数字电子 - 快速指南

- 数字电子 - 资源

- 数字电子 - 讨论

数字电子中的与门

在数字电子学中,有几种不同类型的逻辑门,例如与门、或门、非门等。在本章中,我们将解释**与门的理论**。

与门是一种基本逻辑门,用于实现各种复杂的数字电路和系统。与门对施加在其上的输入执行逻辑乘法,并相应地产生输出。

什么是与门?

**与门**是一种用于各种数字电路和系统中的基本逻辑门类型。仅当所有输入都为高电平或逻辑1或真时,它才会产生高电平或逻辑1或真的输出。对于所有其他输入组合,它都会产生低电平或逻辑0或假的输出。

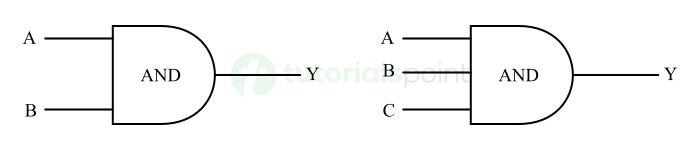

两个和三个输入与门的逻辑符号如下图所示。

这里,**A、B**和**C**是输入变量,**Y**是输出变量。

在本章中,我们将仅介绍具有三个输入的与门。但我们可以为任意数量的输入变量设计与门。

与门的真值表

与门的真值表包含输入和输出,并指定它们之间的关系。

双输入与门的真值表如下所示:

| 输入 | 输出 | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

从双输入与门的这个真值表中可以看出,只有当两个输入都为逻辑1或高电平时,与门的输出才为逻辑1或高电平。

下表表示**三输入与门**的真值表:

| 输入 | 输出 | ||

|---|---|---|---|

| A | B | C | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

此真值表显示,只有当与门的所有三个输入都为高电平或逻辑1时,输出才为高电平或逻辑1。对于其余输入组合,输出为低电平或逻辑0。

从这些与门的真值表中,我们可以得出结论:只有当所有输入都为高电平或逻辑1时,与门才会产生高电平或逻辑1的输出,否则输出为低电平或逻辑0。

与门的工作原理

双输入与门的工作原理如下所示:

- 如果A = 0且B = 0,则输出为低电平,即Y = 0。

- 如果A = 0且B = 1,则输出为低电平,即Y = 0。

- 如果A = 1且B = 0,则输出为低电平,即Y = 0。

- 如果A = 1且B = 1,则输出为高电平,即Y = 1。

三输入与门的工作原理如下所示:

- 如果A = 0,B = 0,C = 0,则输出为低电平,即Y = 0。

- 如果A = 0,B = 0,C = 1,则输出为低电平,即Y = 0。

- 如果A = 0,B = 1,C = 0,则输出为低电平,即Y = 0。

- 如果A = 0,B = 1,C = 1,则输出为低电平,即Y = 0。

- 如果A = 1,B = 0,C = 0,则输出为低电平,即Y = 0。

- 如果A = 1,B = 0,C = 1,则输出为低电平,即Y = 0。

- 如果A = 1,B = 1,C = 0,则输出为低电平,即Y = 0。

- 如果A = 1,B = 1,C = 1,则输出为高电平,即Y = 1。

这就是关于双输入和三输入与门工作原理的所有内容。

与门的布尔表达式

布尔表达式是一个逻辑方程或逻辑函数,它表示与门输入和输出之间的数学关系。

双输入与门的布尔表达式由下式给出:

Y = A · B

其中,**A**和**B**是输入,**Y**是输出。此表达式读作“Y等于A与B”。点 (·) 符号表示与运算。

对于三输入与门,布尔表达式由下式给出:

Y = A · B · C

它读作“Y等于A与B与C”。

以同样的方式,我们可以获得具有任意数量输入变量的与门的布尔表达式。

使用晶体管的与门

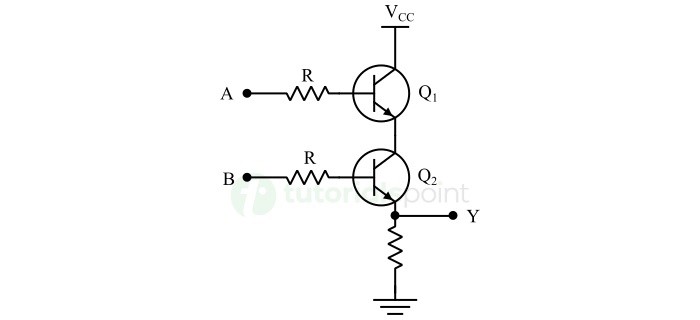

双输入与门的晶体管电路如下图所示。

使用晶体管实现与门需要与输入数量一样多的晶体管。例如,双输入与门需要两个晶体管。

晶体管与门的工作原理

上面图中所示的晶体管与门的工作原理如下所述:

**当两个输入A和B都为低电平时**,晶体管Q1和Q2保持关闭状态并充当开路开关。因此,输出线Y将直接连接到接地电位。因此,输出为低电平或逻辑0。

**当输入A为低电平且输入B为高电平时**,第一个晶体管Q1关闭,第二个晶体管Q2打开。但电源电压仍然不会连接到输出线,输出线将保持接地电位。因此,输出为低电平或逻辑0。

**当输入A为高电平且输入B为低电平时**,晶体管Q1将导通,晶体管Q2将保持关闭状态。在这种情况下,输出线不会接收电源电压,而是连接到接地电位。因此,对于这种输入组合,输出为低电平或逻辑0。

**当两个输入A和B都为高电平时**,两个晶体管Q1和Q2都将打开并充当闭合开关。在这种情况下,电源电压直接连接到输出线。这使得电路的输出为高电平或逻辑1。

这就是上面晶体管电路如何充当双输入与门。我们可以添加更多晶体管来实现高阶与门。

使用开关的与门

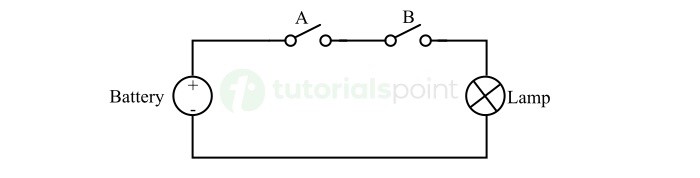

我们还可以使用电池、开关和灯泡或灯泡来实现与门逻辑。下图显示了使用开关的与门。

在这个与门电路中,我们有一个电压源,两个开关代表与门的两个输入端,一个灯泡代表输出。

从电路图可以看出,如果开关A和B都闭合,电流就会有闭合回路可以流动。因此,灯泡会亮起,表示高电平或逻辑1输出。

如果两个开关中的任何一个或两个都断开,电流路径就会断开,导致灯泡熄灭。这表示与门输出的低电平或逻辑0状态。

这样,上面所示的开关电路就实现了与门运算。通过串联增加更多开关,我们可以实现更高阶的与门。

与门IC

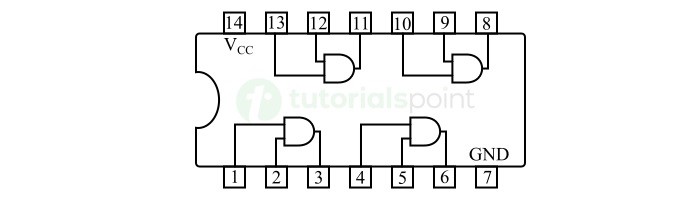

在实际应用中,有一种名为IC 7408的集成电路,它是最常用的与门IC。这种与门IC采用晶体管-晶体管逻辑(TTL)实现。与门IC 7408的框图如下所示。

它是一个四2输入与门IC,在一个芯片上集成了四个双输入与门。它有14个引脚。

结论

总之,与门是一种基本的逻辑门,用于数字电路中实现布尔乘法运算。

只有当与门的所有输入都为高电平或逻辑1时,其输出才为高电平或逻辑1。否则,它会产生低电平或逻辑0输出。

与门在各种数字电子应用中发挥着重要作用,例如数据处理、存储器设备、算术逻辑单元、控制系统等等。