- Digital Electronics Tutorial

- Digital Electronics - Home

- Digital Electronics Basics

- Types of Digital Systems

- Types of Signals

- Logic Levels And Pulse Waveforms

- Digital System Components

- Digital Logic Operations

- Digital Systems Advantages

- Number Systems

- Number Systems

- Binary Numbers Representation

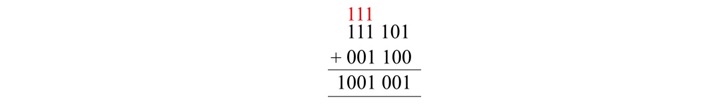

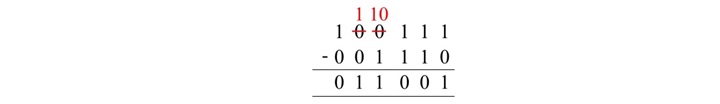

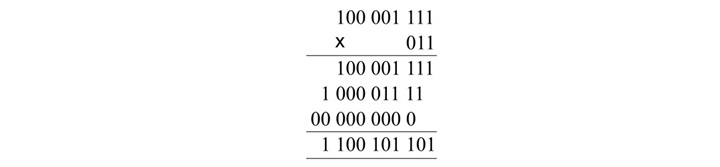

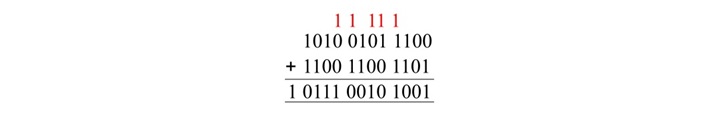

- Binary Arithmetic

- Signed Binary Arithmetic

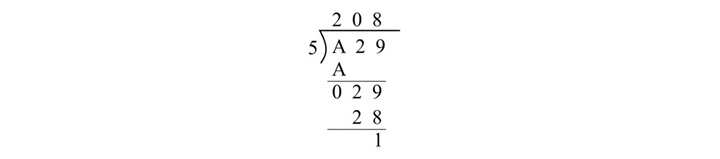

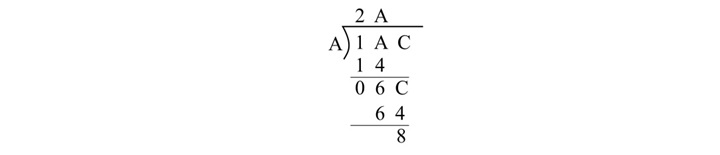

- Octal Arithmetic

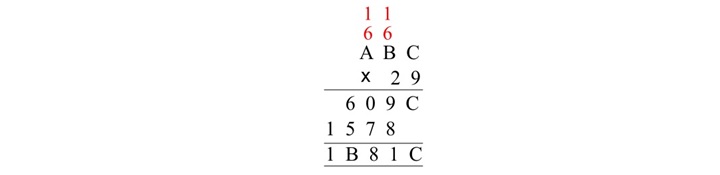

- Hexadecimal Arithmetic

- Complement Arithmetic

- Base Conversions

- Base Conversions

- Binary to Decimal Conversion

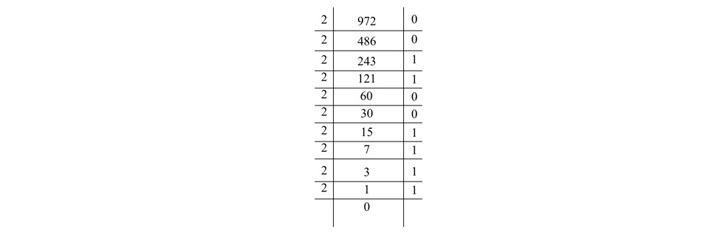

- Decimal to Binary Conversion

- Binary to Octal Conversion

- Octal to Binary Conversion

- Octal to Decimal Conversion

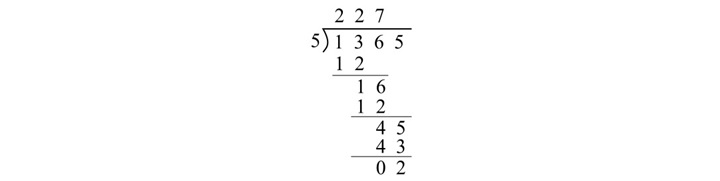

- Decimal to Octal Conversion

- Hexadecimal to Binary Conversion

- Binary to Hexadecimal Conversion

- Hexadecimal to Decimal Conversion

- Decimal to Hexadecimal Conversion

- Octal to Hexadecimal Conversion

- Hexadecimal to Octal Conversion

- Binary Codes

- Binary Codes

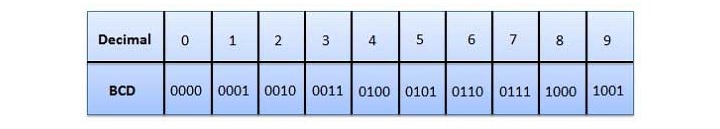

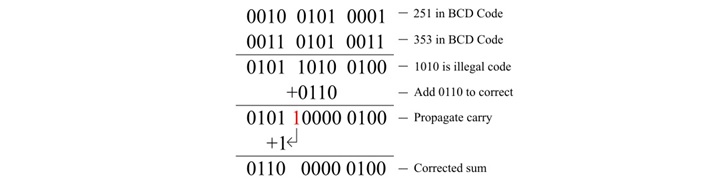

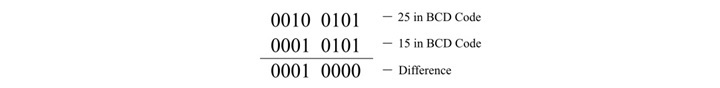

- 8421 BCD Code

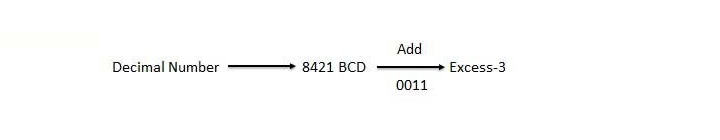

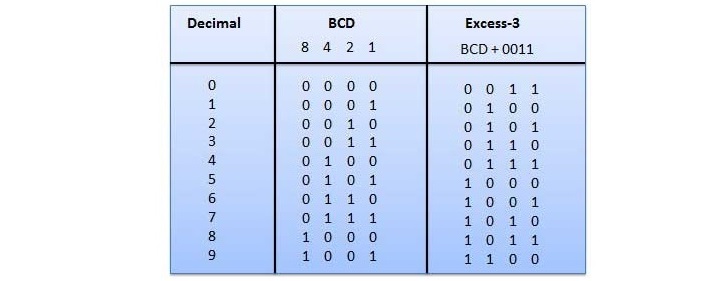

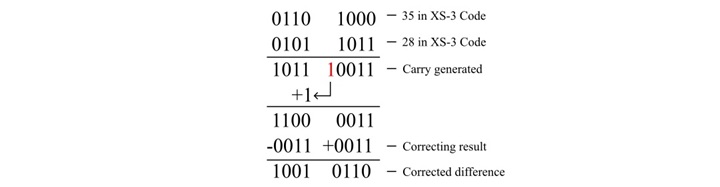

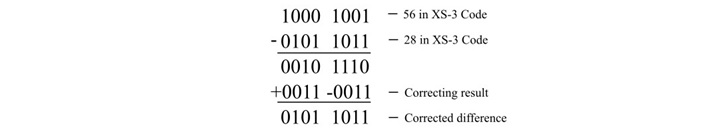

- Excess-3 Code

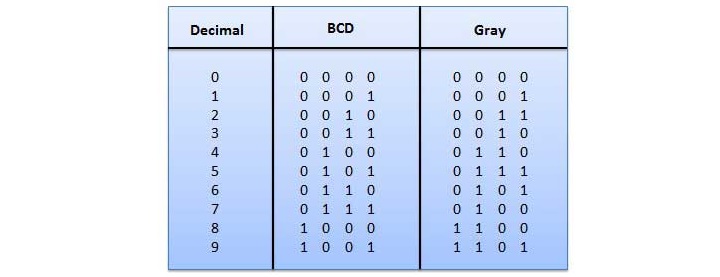

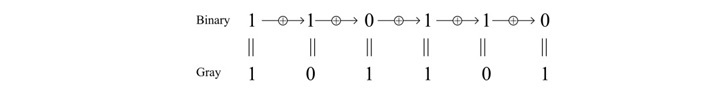

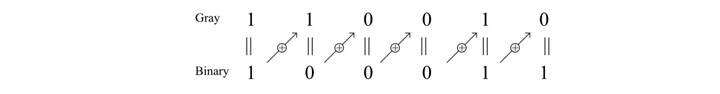

- Gray Code

- ASCII Codes

- EBCDIC Code

- Code Conversion

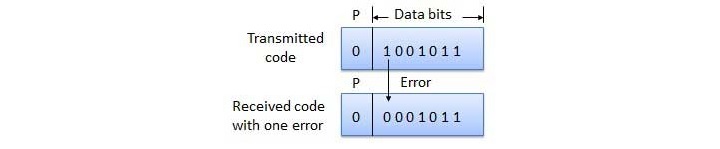

- Error Detection & Correction Codes

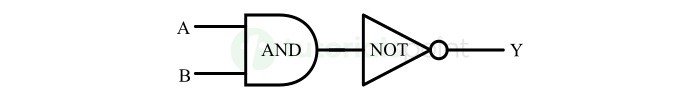

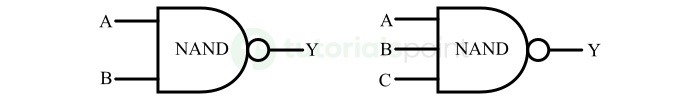

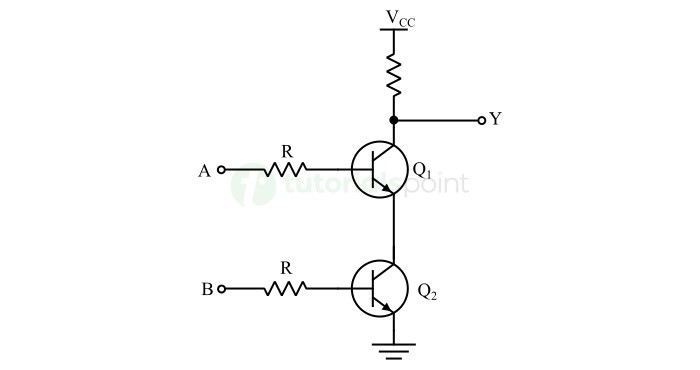

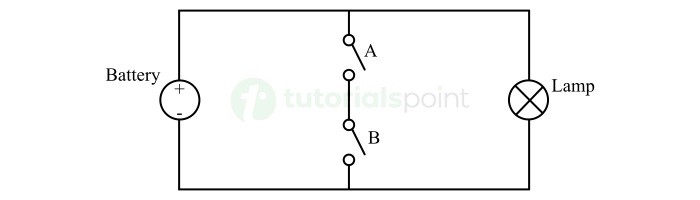

- Logic Gates

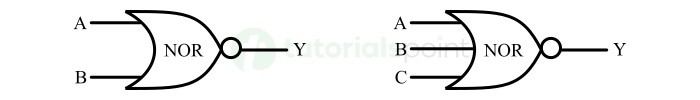

- Logic Gates

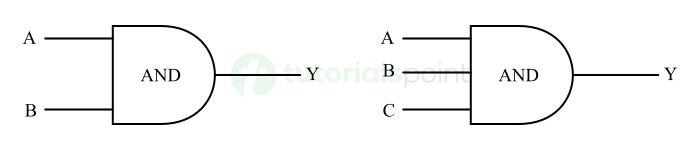

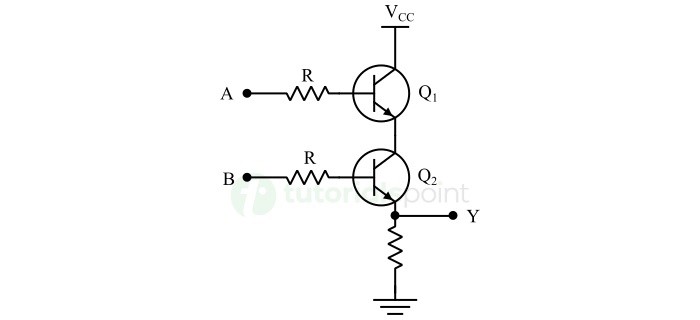

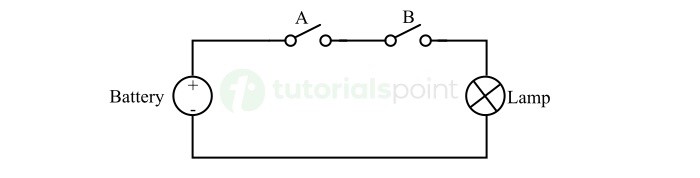

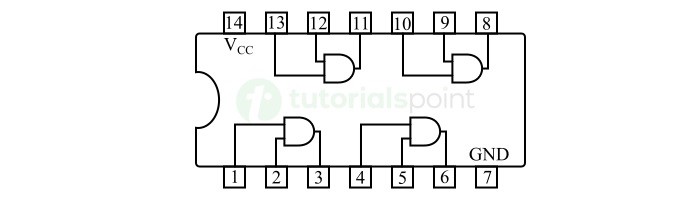

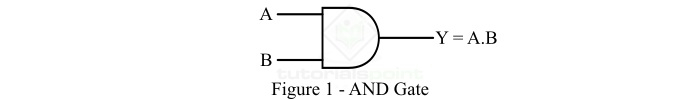

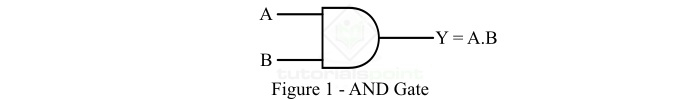

- AND Gate

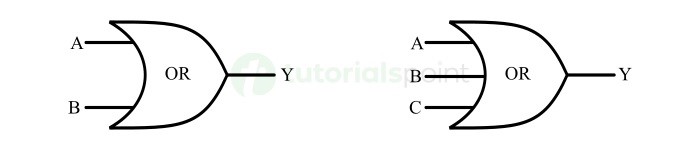

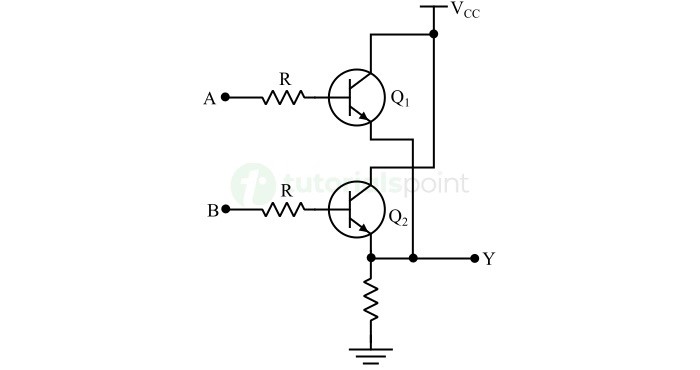

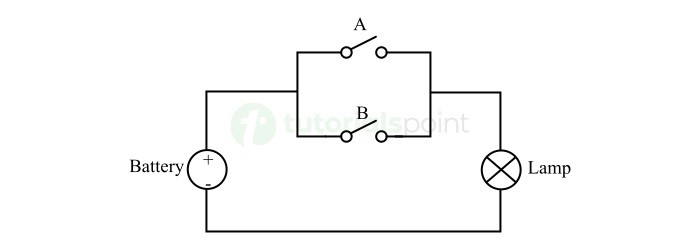

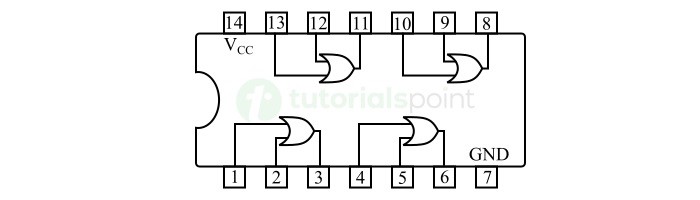

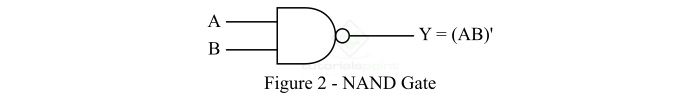

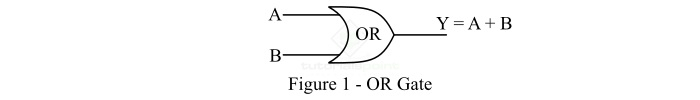

- OR Gate

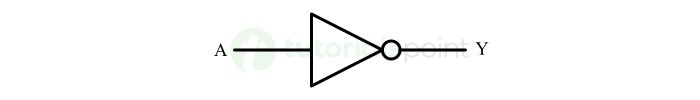

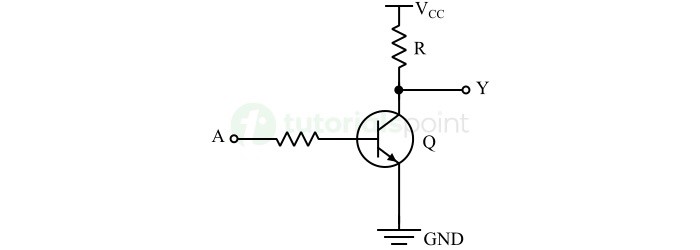

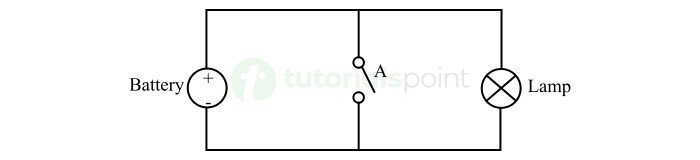

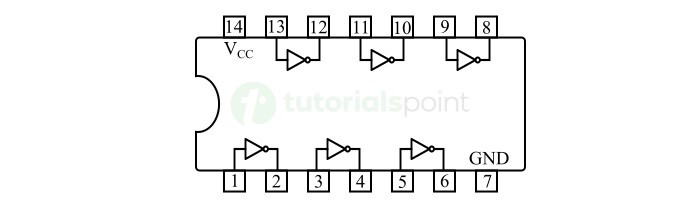

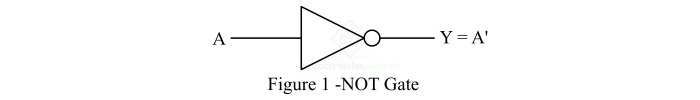

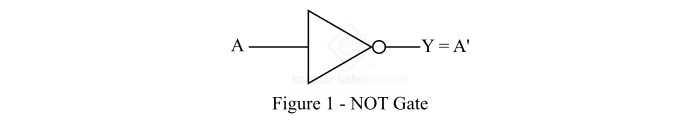

- NOT Gate

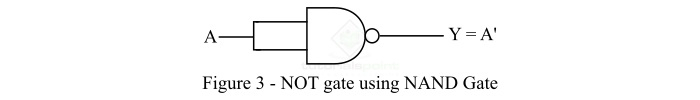

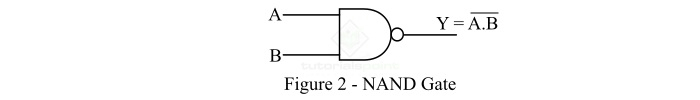

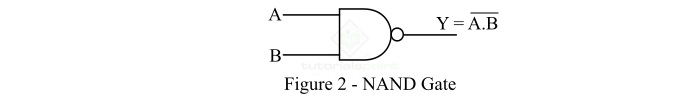

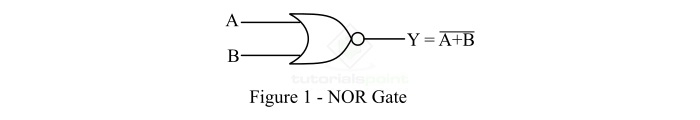

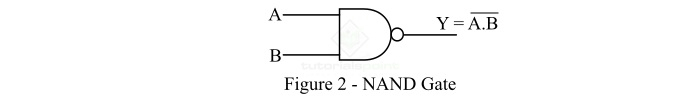

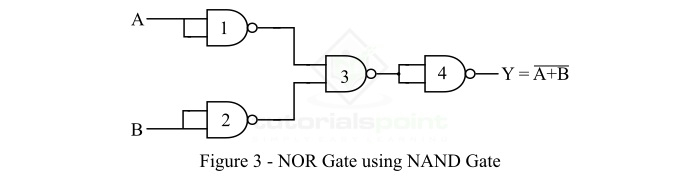

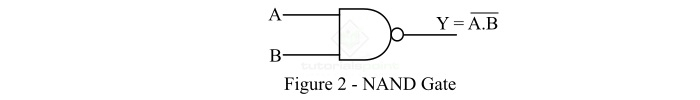

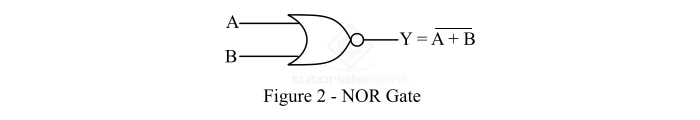

- Universal Gates

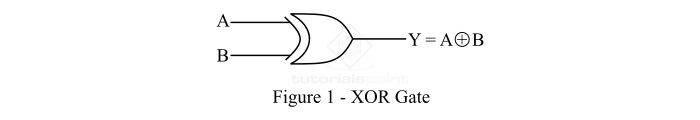

- XOR Gate

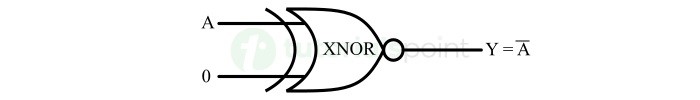

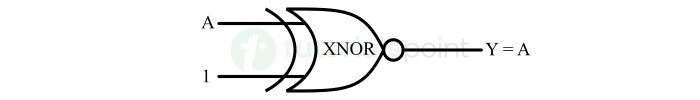

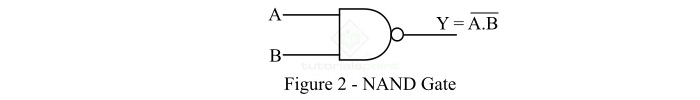

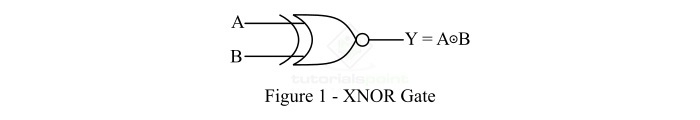

- XNOR Gate

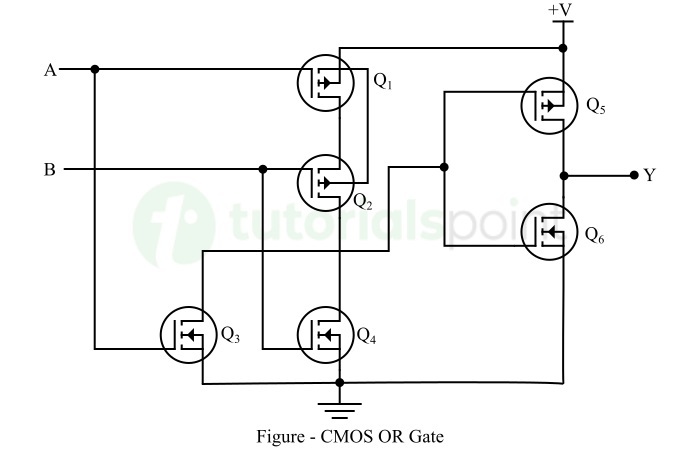

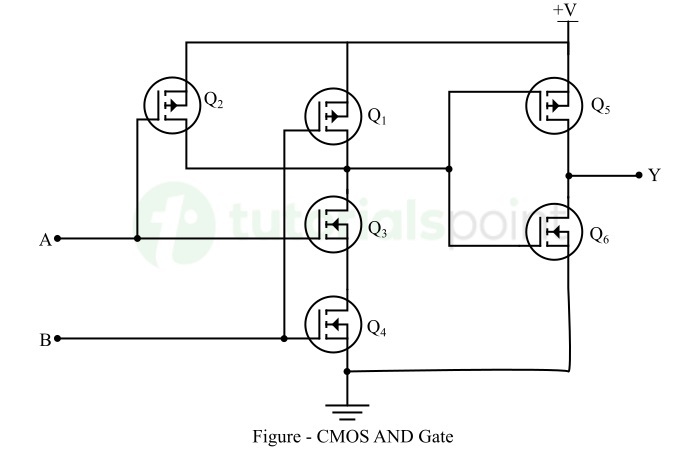

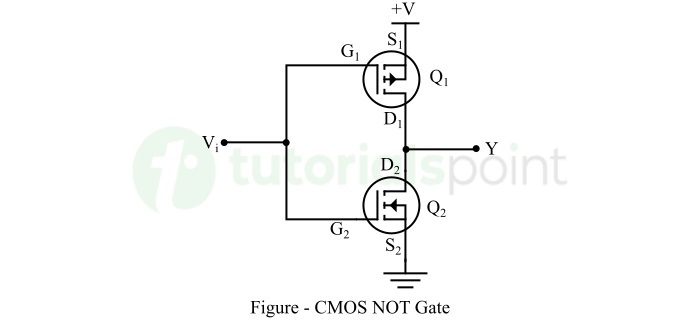

- CMOS Logic Gate

- OR Gate Using Diode Resistor Logic

- AND Gate vs OR Gate

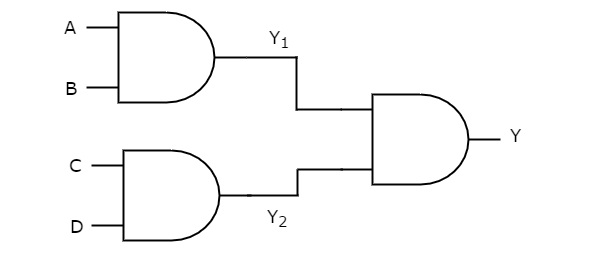

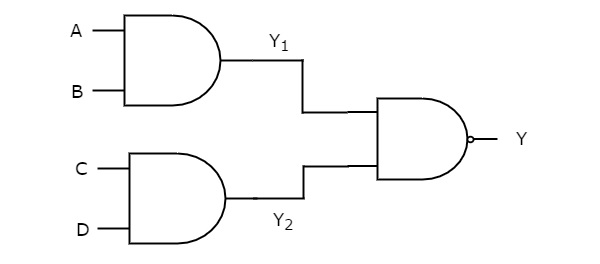

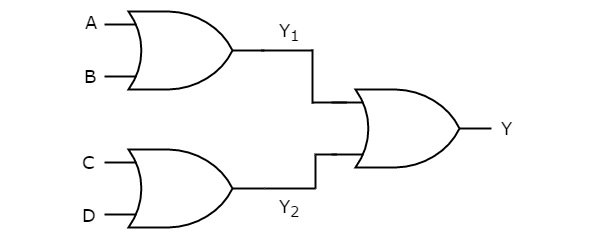

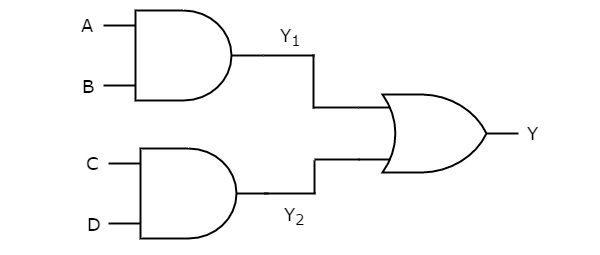

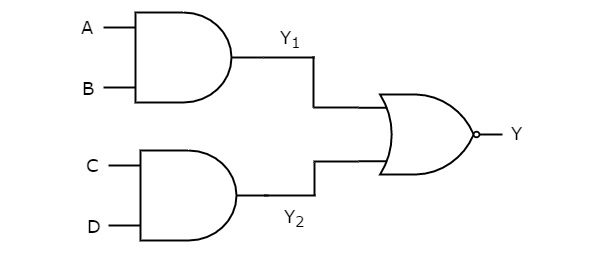

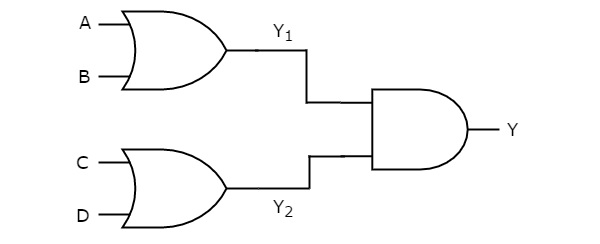

- Two Level Logic Realization

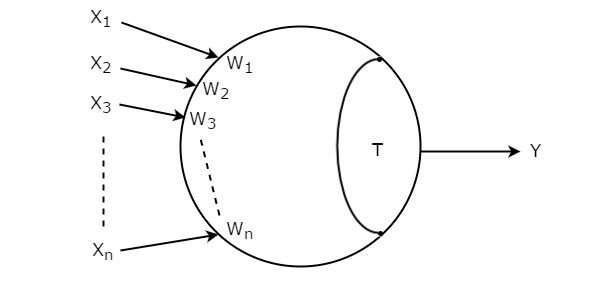

- Threshold Logic

- Boolean Algebra

- Boolean Algebra

- Laws of Boolean Algebra

- Boolean Functions

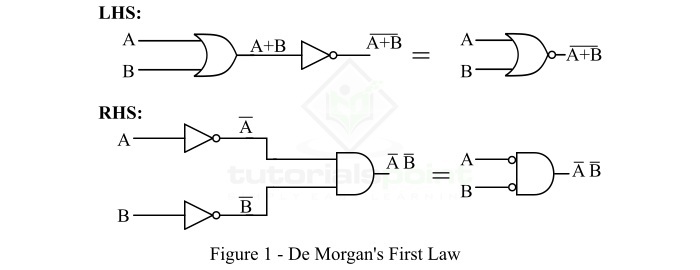

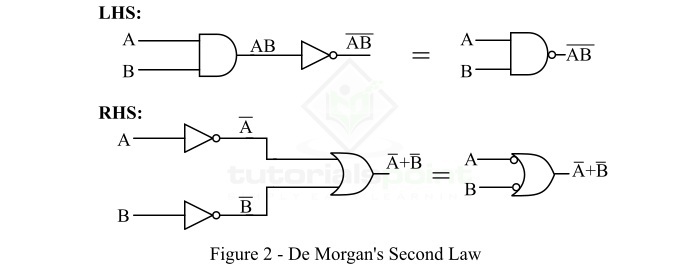

- DeMorgan's Theorem

- SOP and POS Form

- POS to Standard POS Form

- Minimization Techniques

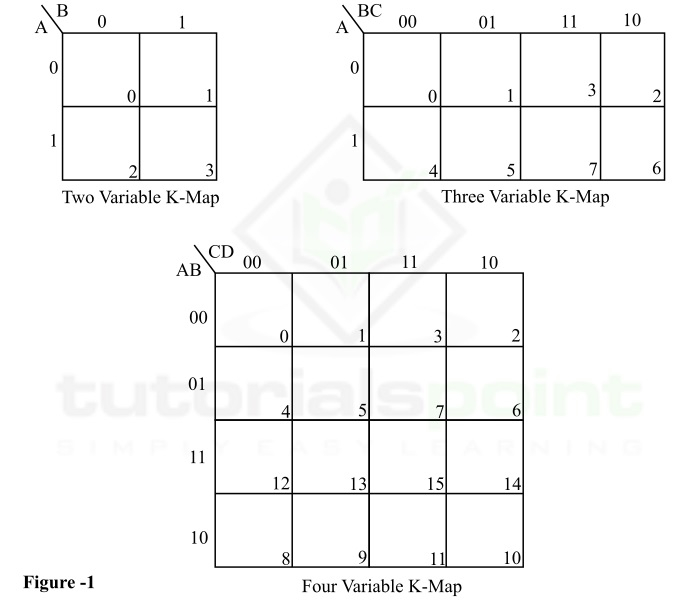

- K-Map Minimization

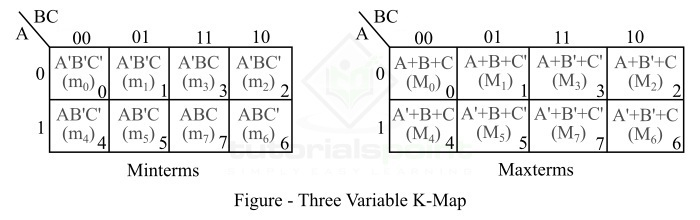

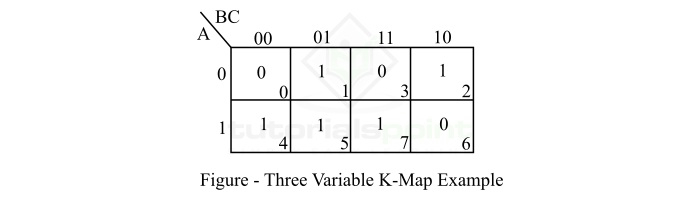

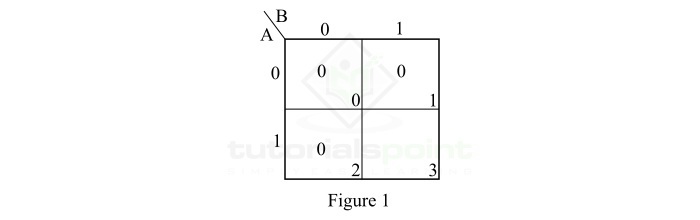

- Three Variable K-Map

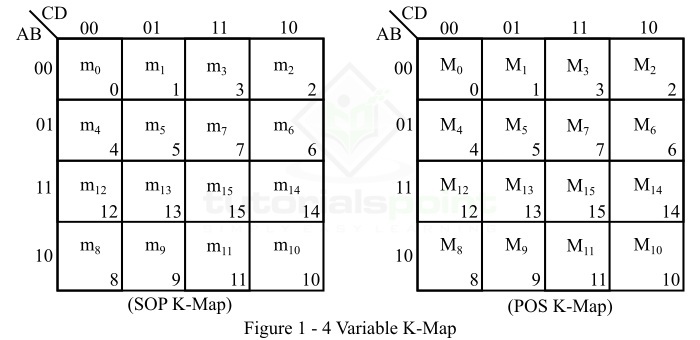

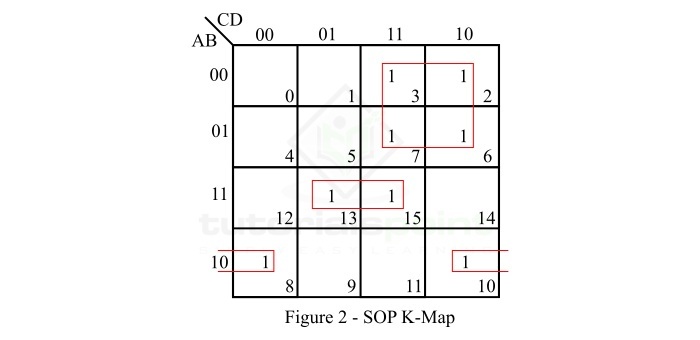

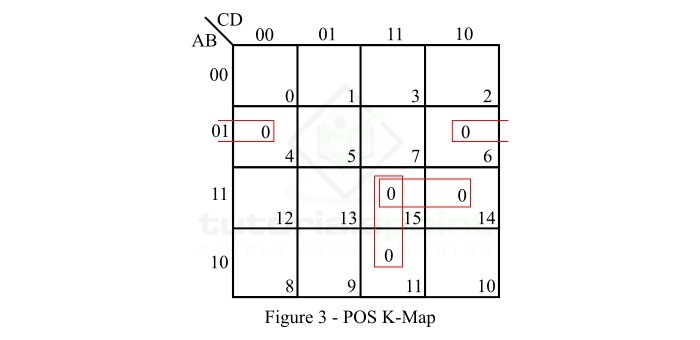

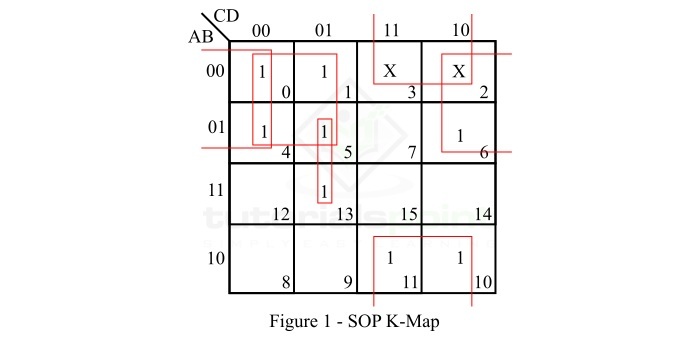

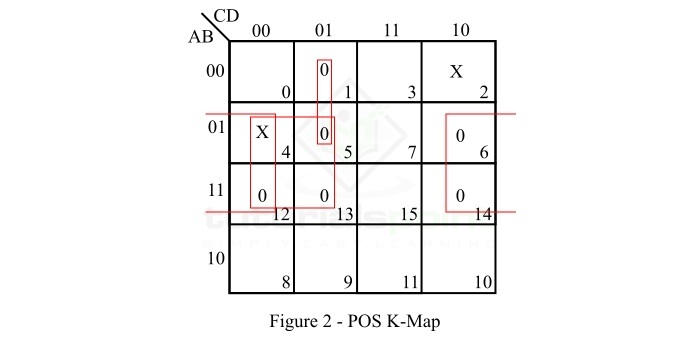

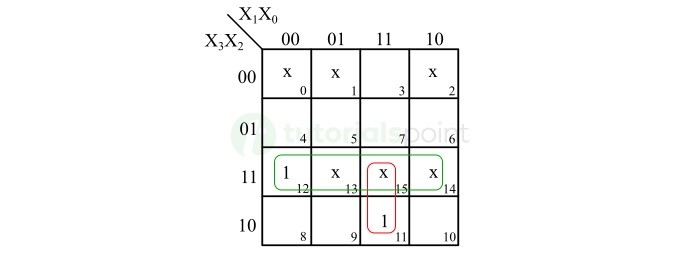

- Four Variable K-Map

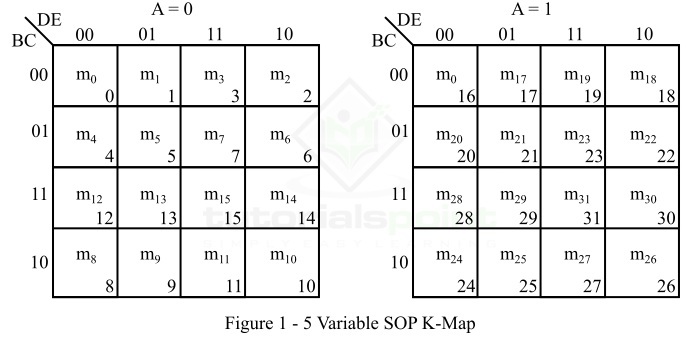

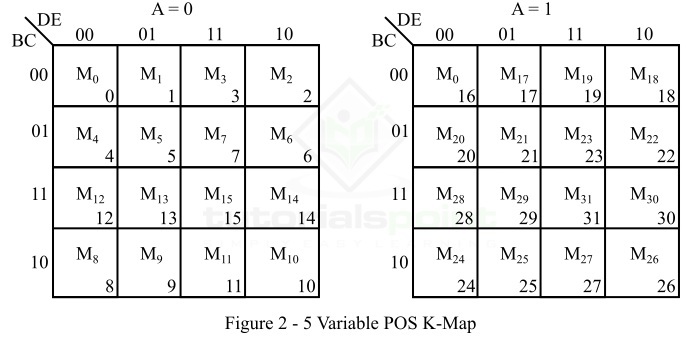

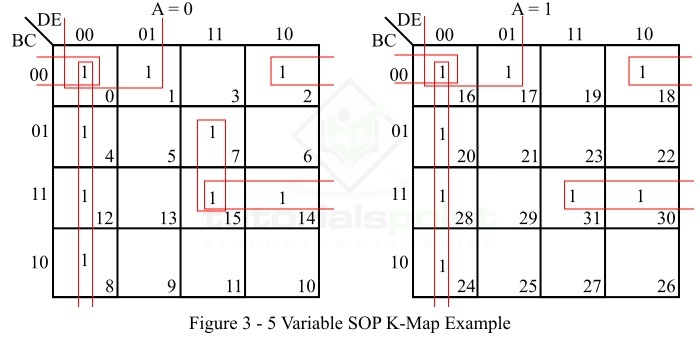

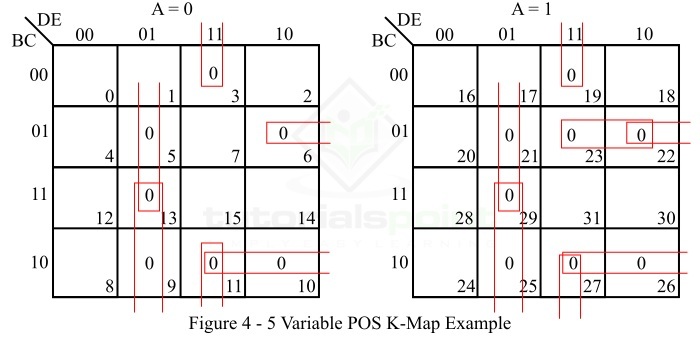

- Five Variable K-Map

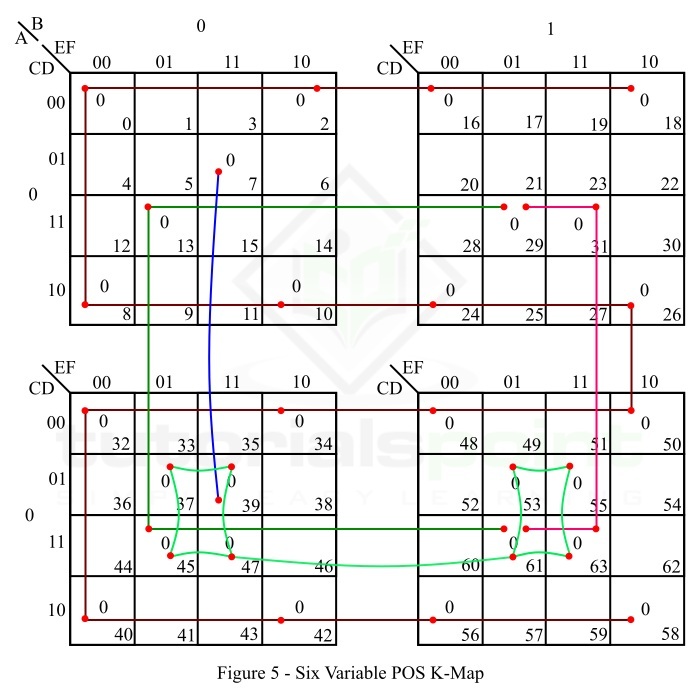

- Six Variable K-Map

- Don't Care Condition

- Quine-McCluskey Method

- Min Terms and Max Terms

- Canonical and Standard Form

- Max Term Representation

- Simplification using Boolean Algebra

- Combinational Logic Circuits

- Digital Combinational Circuits

- Digital Arithmetic Circuits

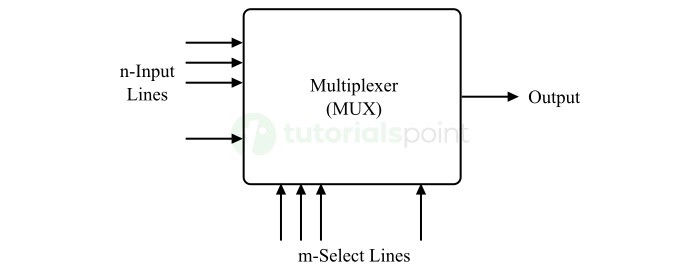

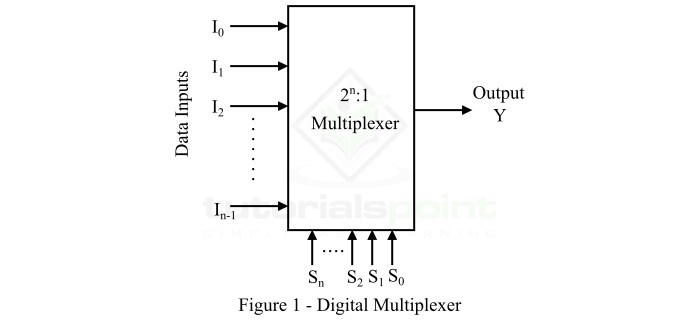

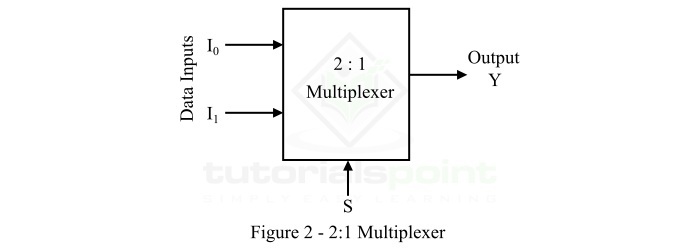

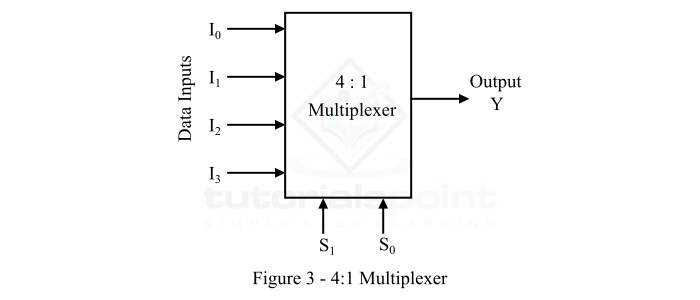

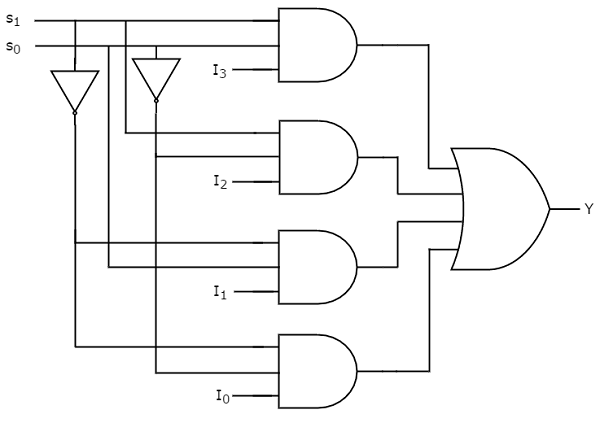

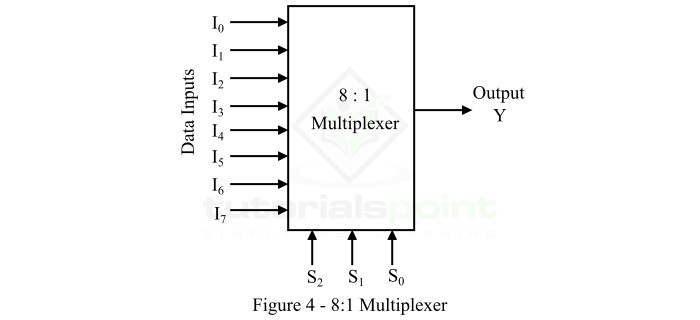

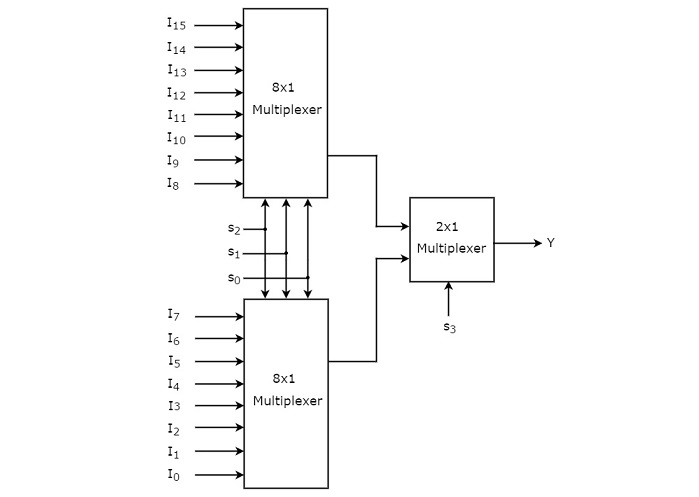

- Multiplexers

- Multiplexer Design Procedure

- Mux Universal Gate

- 2-Variable Function Using 4:1 Mux

- 3-Variable Function Using 8:1 Mux

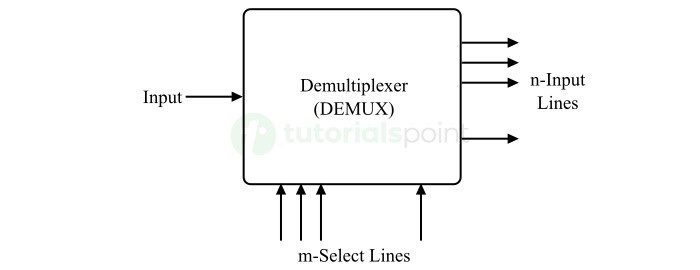

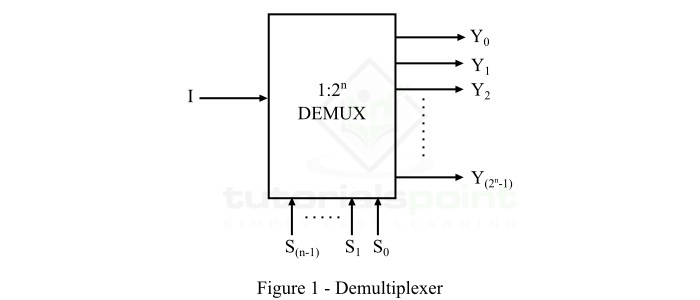

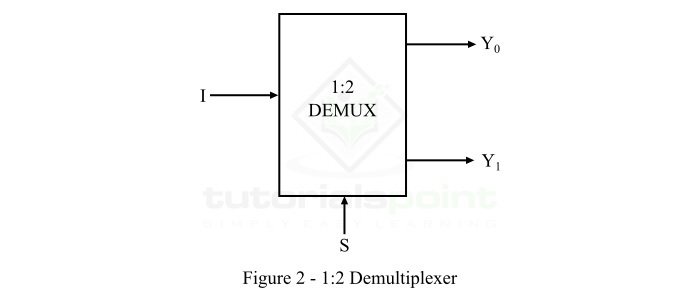

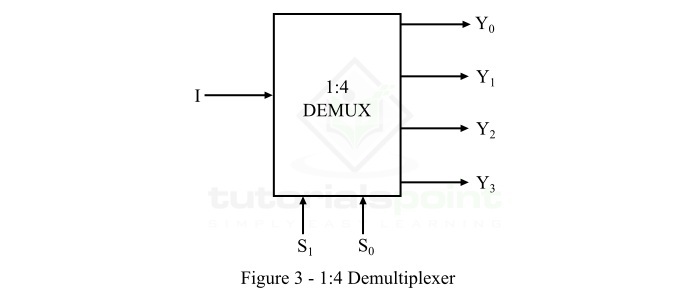

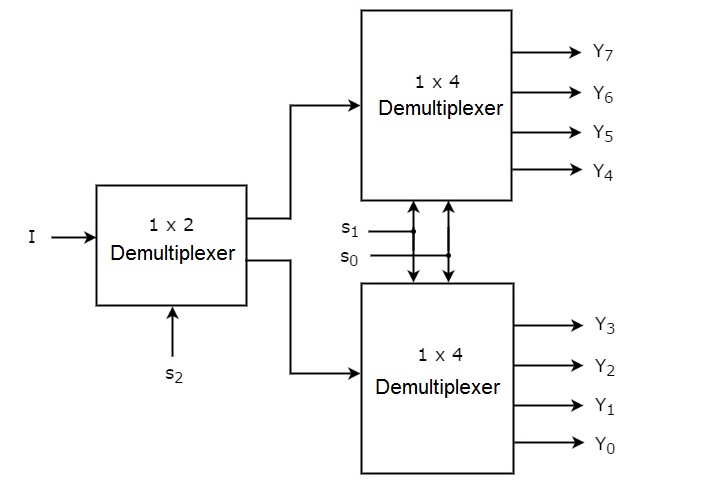

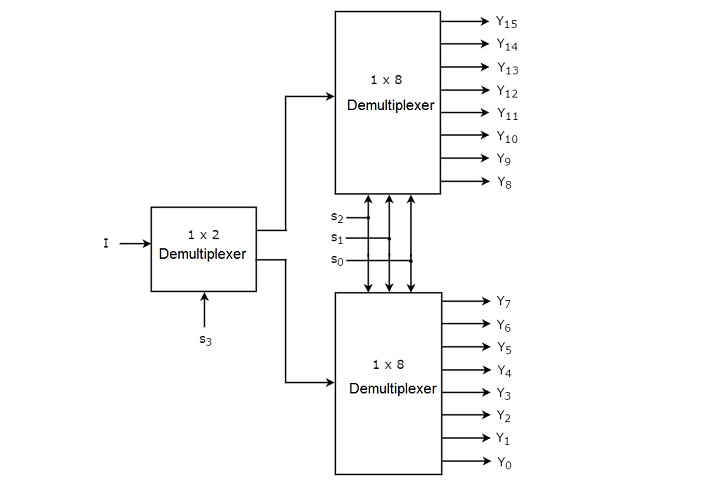

- Demultiplexers

- Mux vs Demux

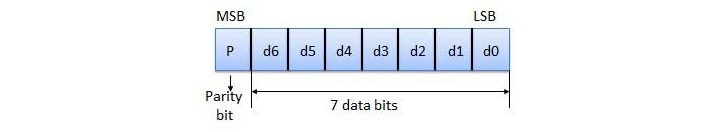

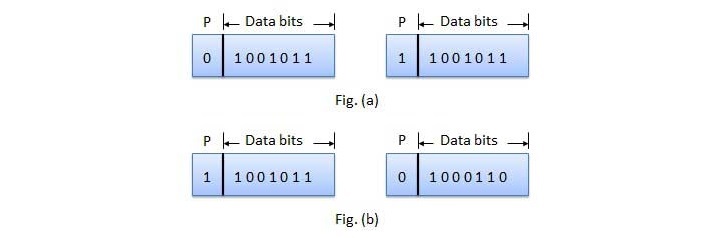

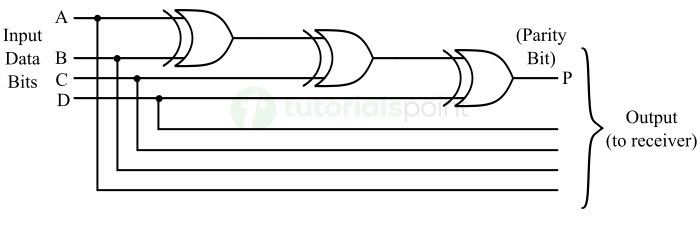

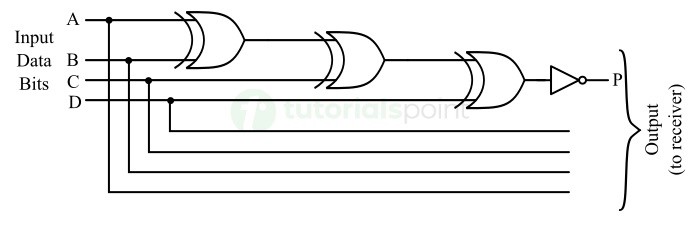

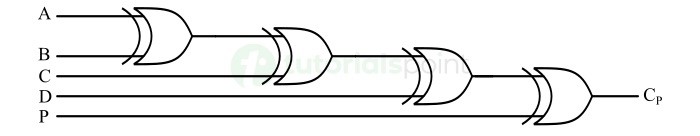

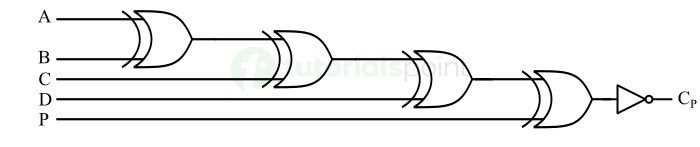

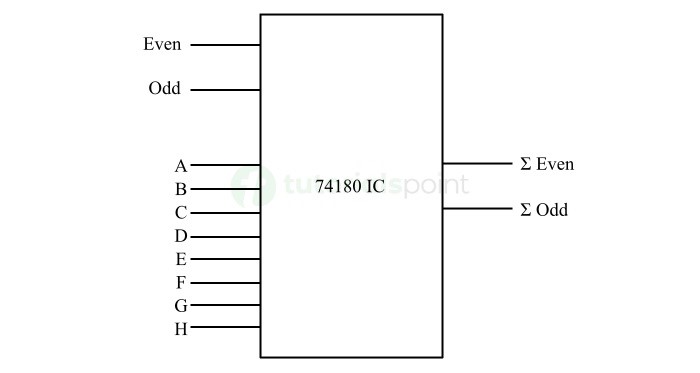

- Parity Bit Generator and Checker

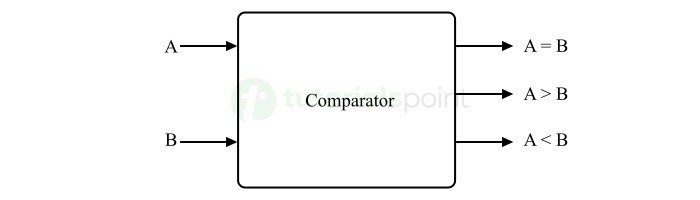

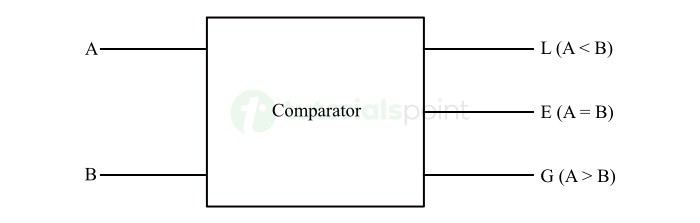

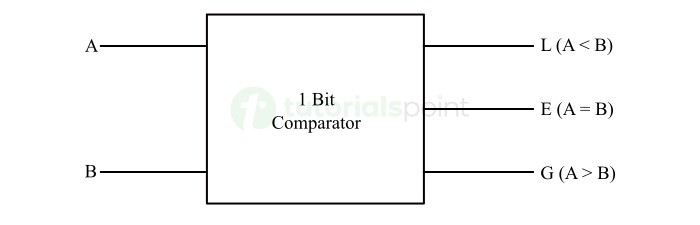

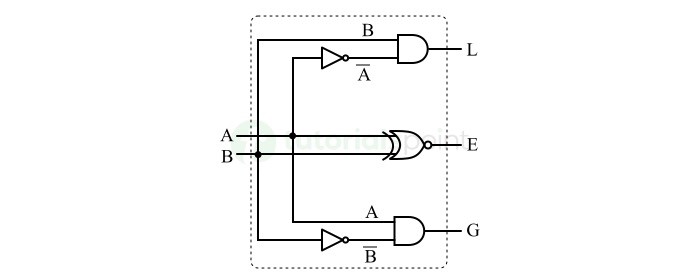

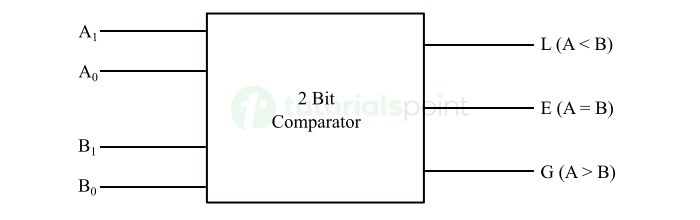

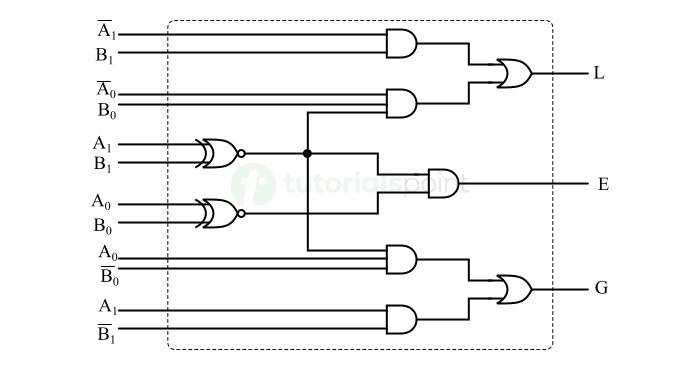

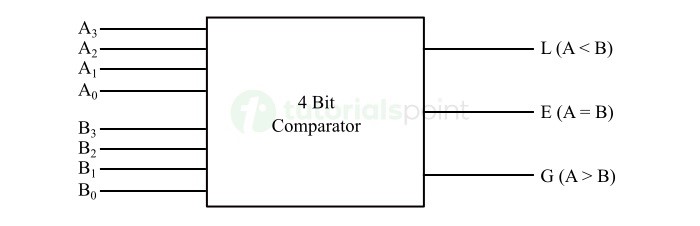

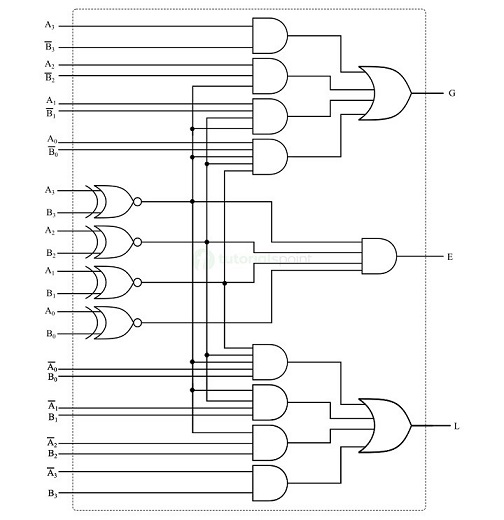

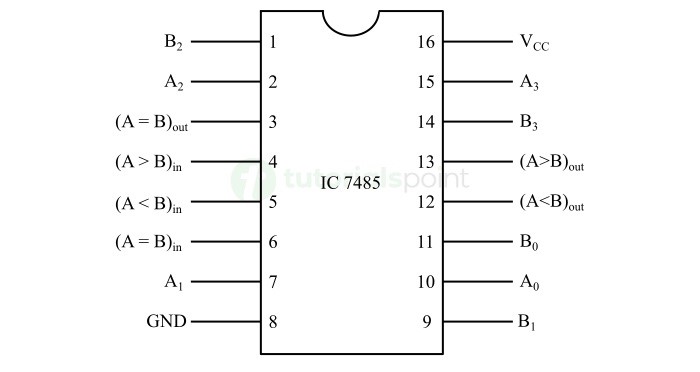

- Comparators

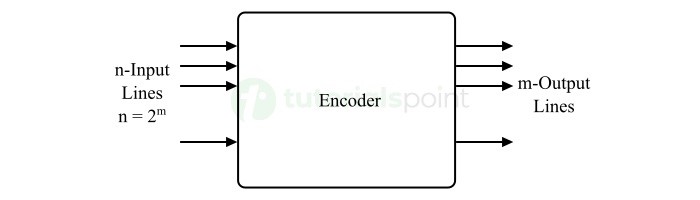

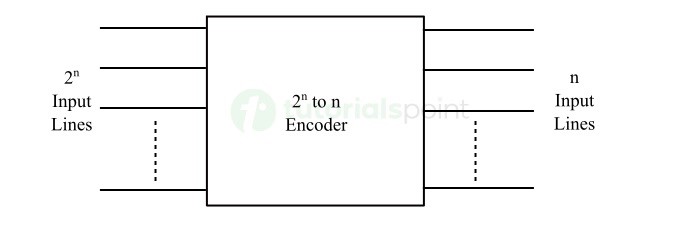

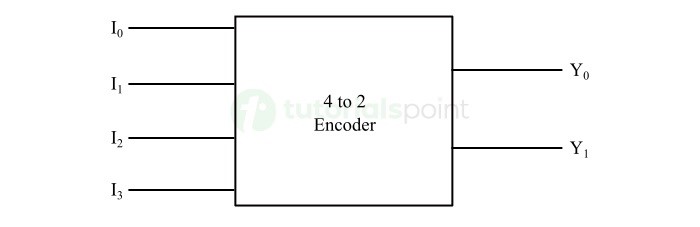

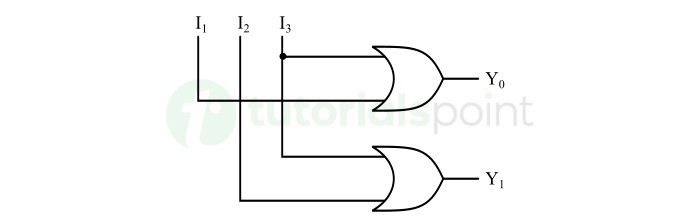

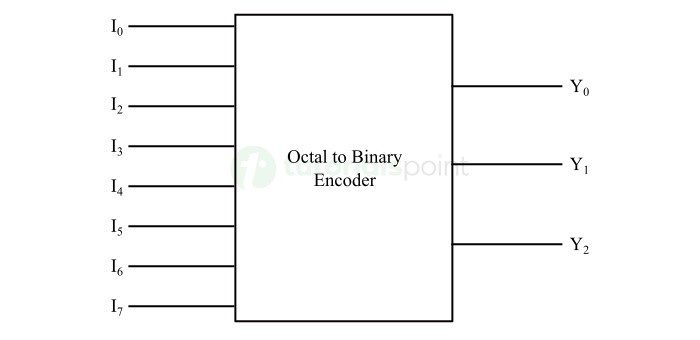

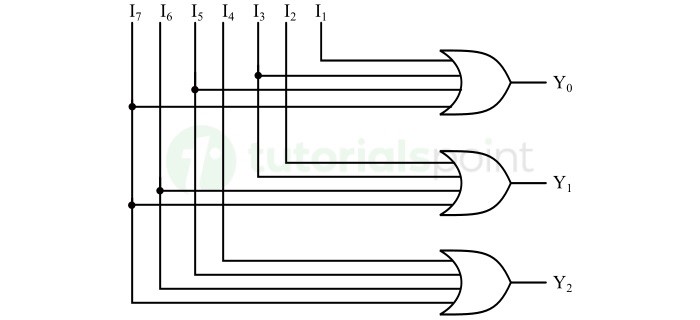

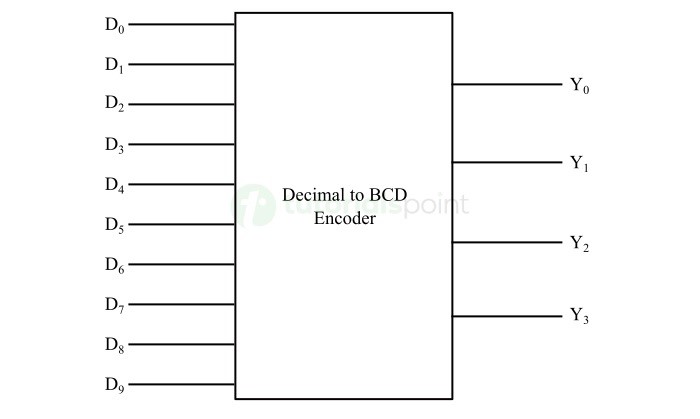

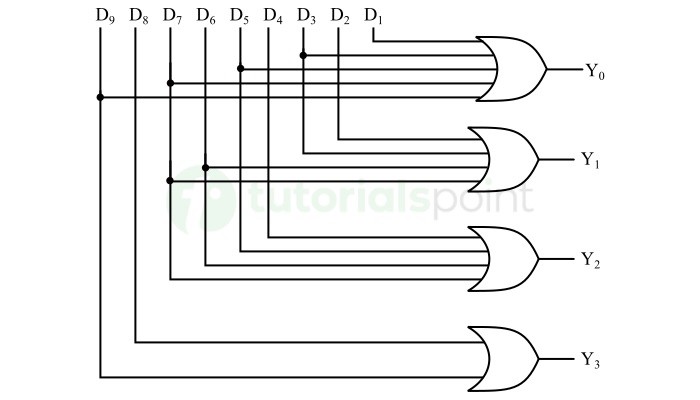

- Encoders

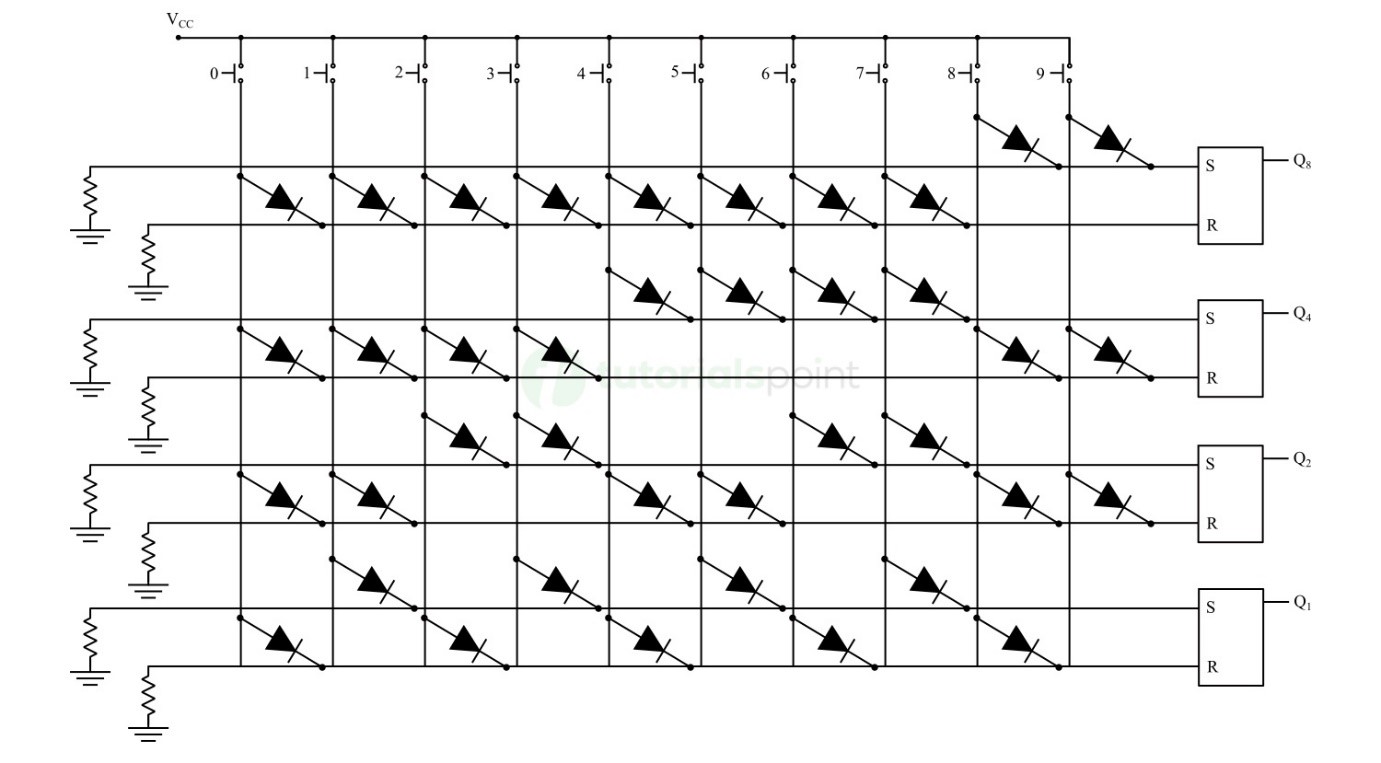

- Keyboard Encoders

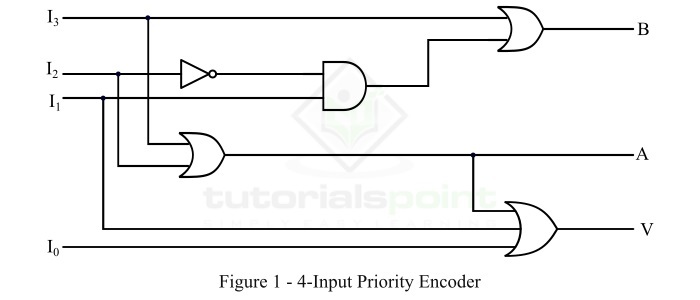

- Priority Encoders

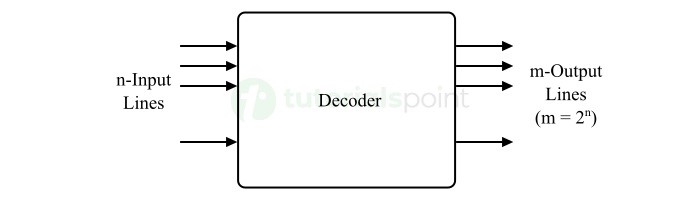

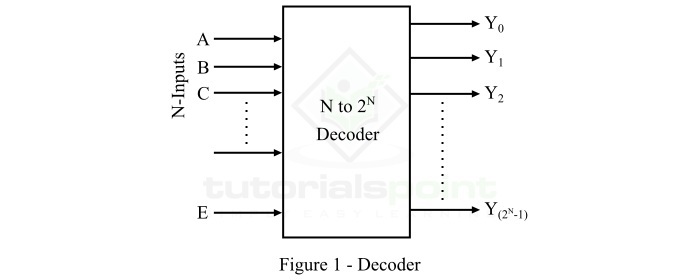

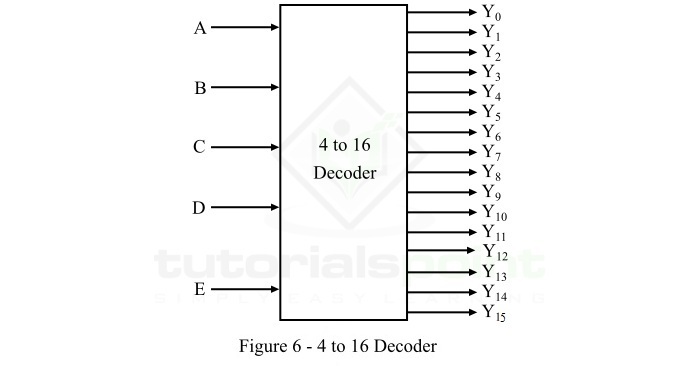

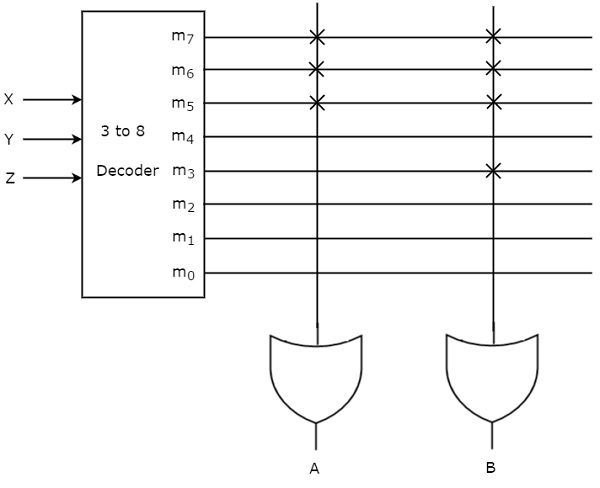

- Decoders

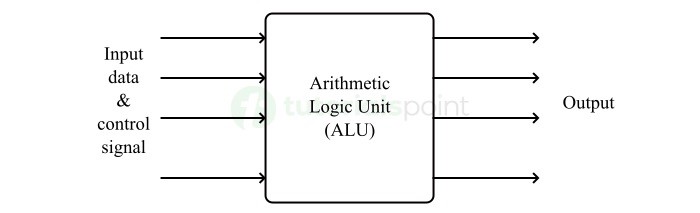

- Arithmetic Logic Unit

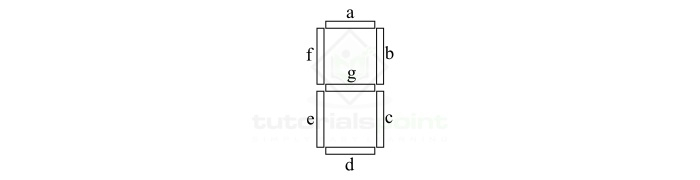

- 7-Segment LED Display

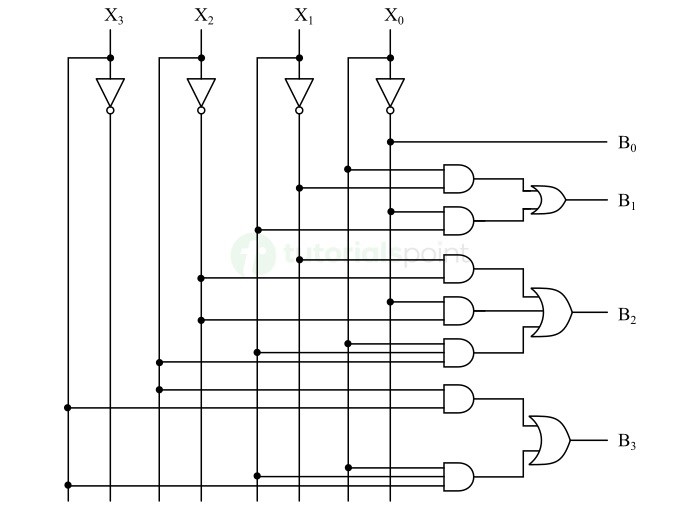

- Code Converters

- Code Converters

- Binary to Decimal Converter

- Decimal to BCD Converter

- BCD to Decimal Converter

- Binary to Gray Code Converter

- Gray Code to Binary Converter

- BCD to Excess-3 Converter

- Excess-3 to BCD Converter

- Adders

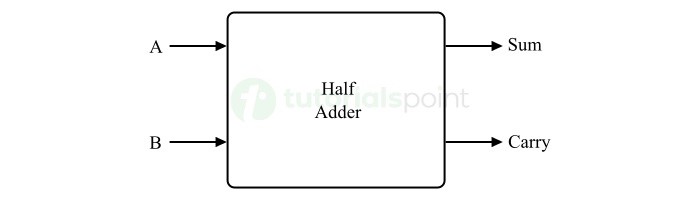

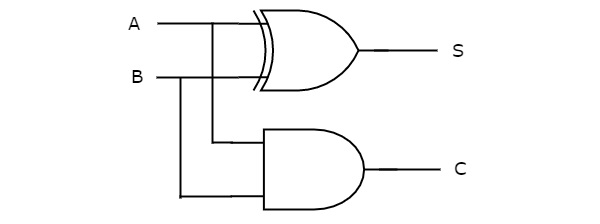

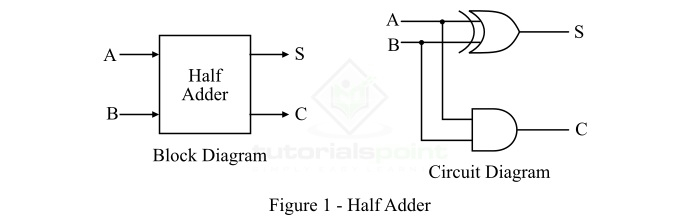

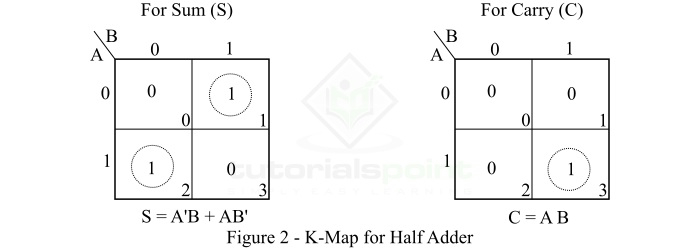

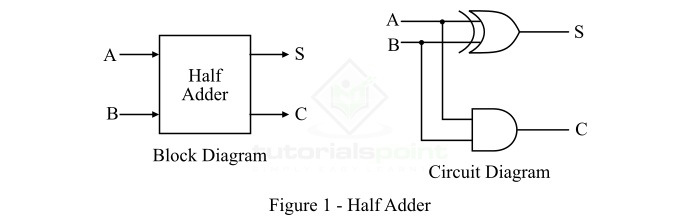

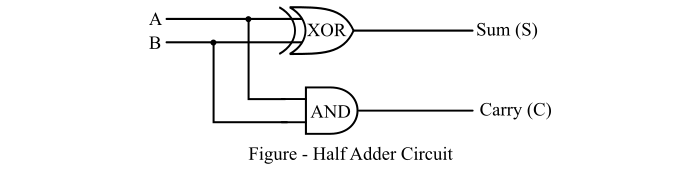

- Half Adders

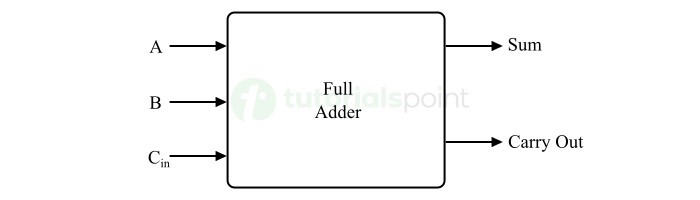

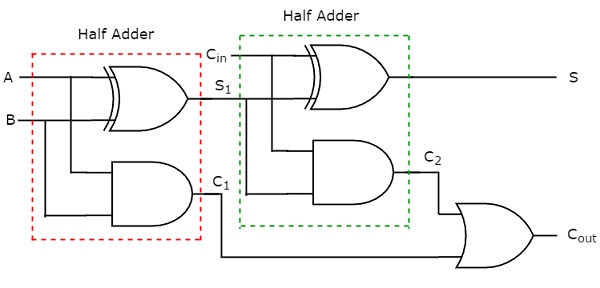

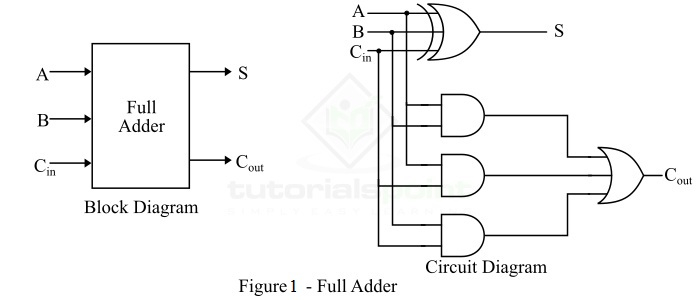

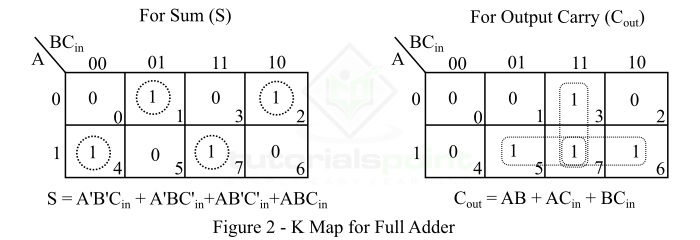

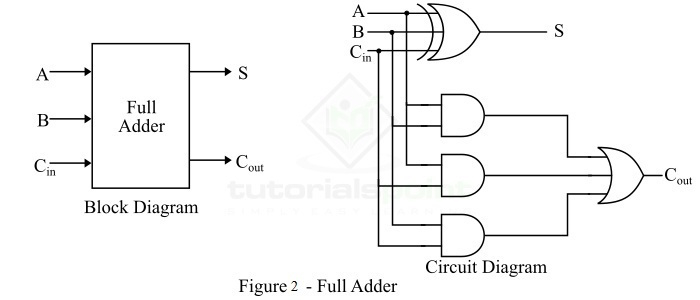

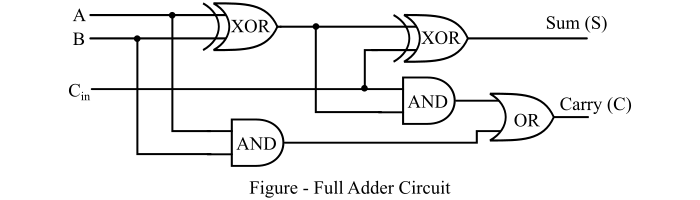

- Full Adders

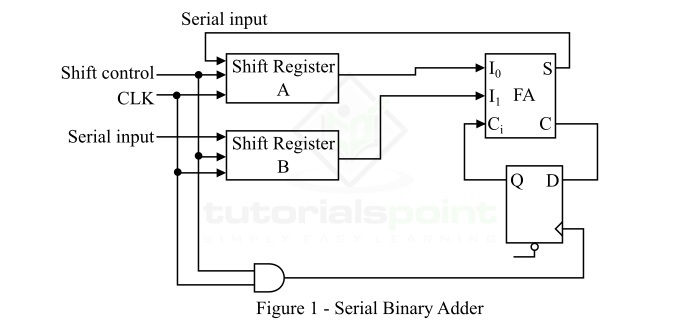

- Serial Adders

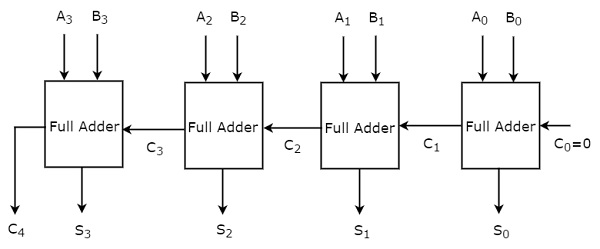

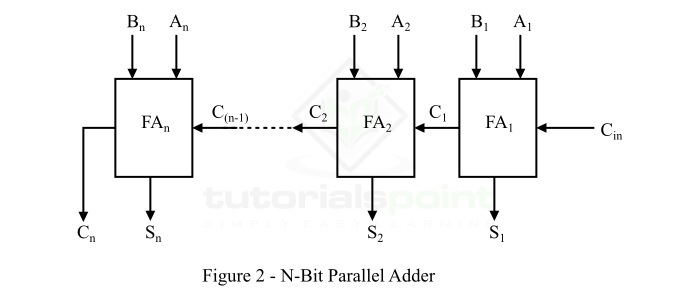

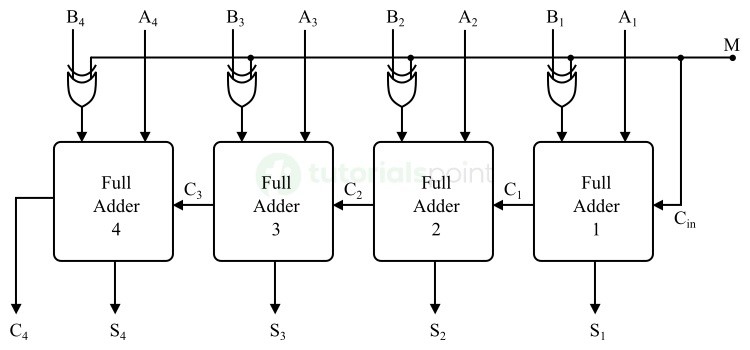

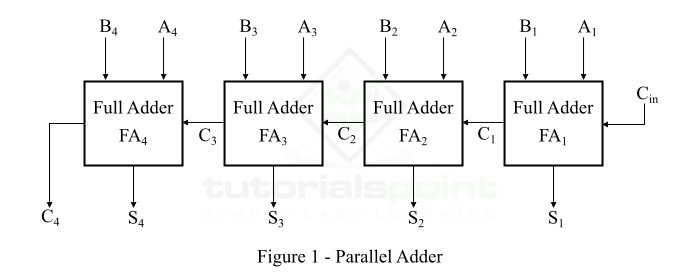

- Parallel Adders

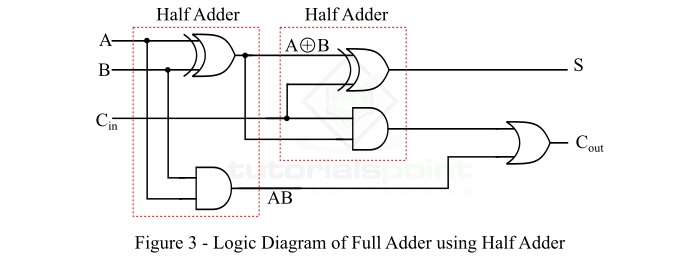

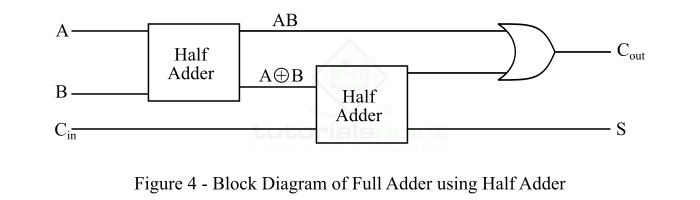

- Full Adder using Half Adder

- Half Adder vs Full Adder

- Full Adder with NAND Gates

- Half Adder with NAND Gates

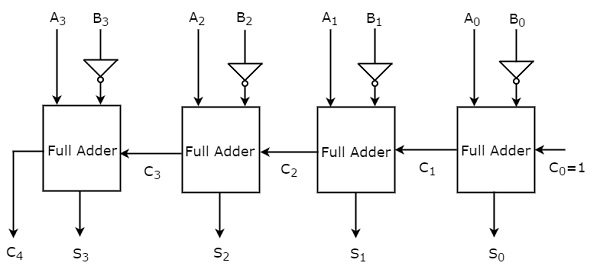

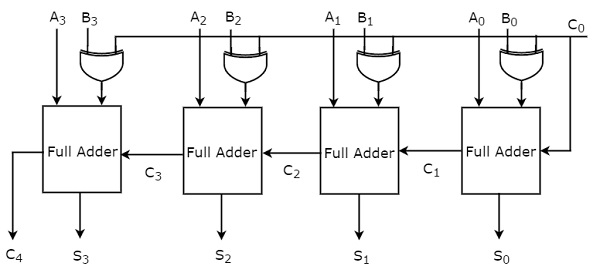

- Binary Adder-Subtractor

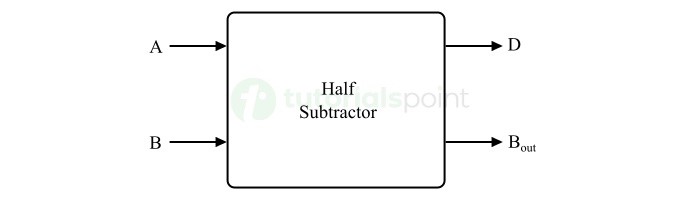

- Subtractors

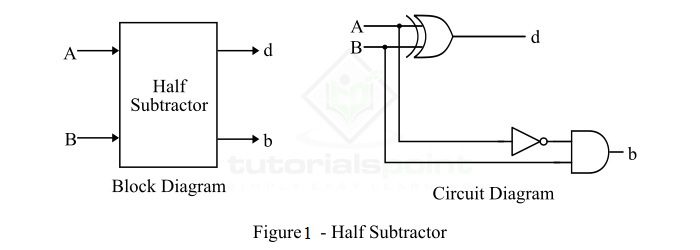

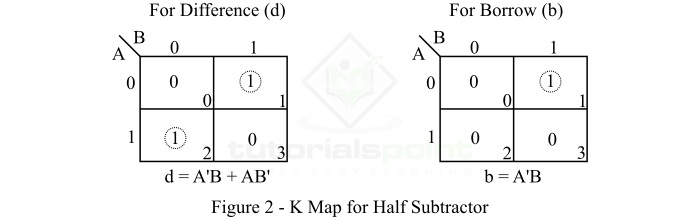

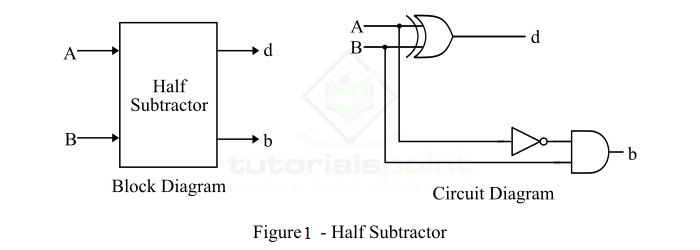

- Half Subtractors

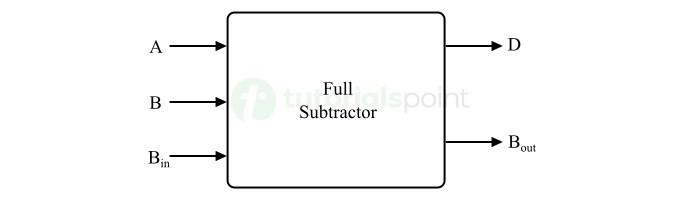

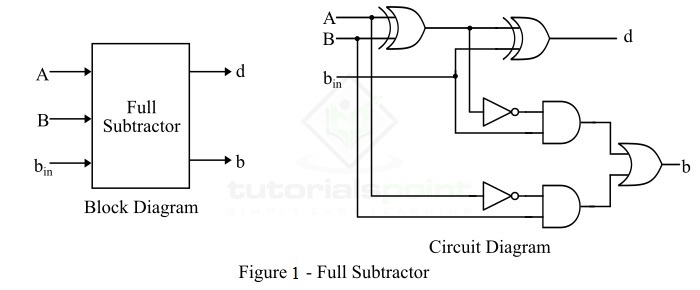

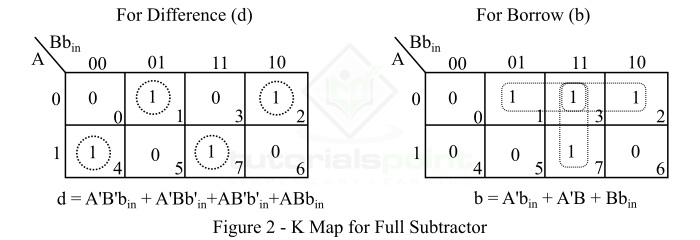

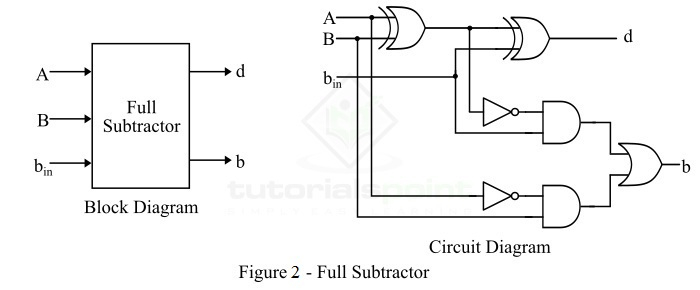

- Full Subtractors

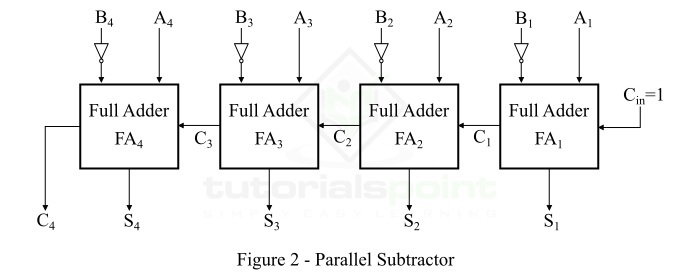

- Parallel Subtractors

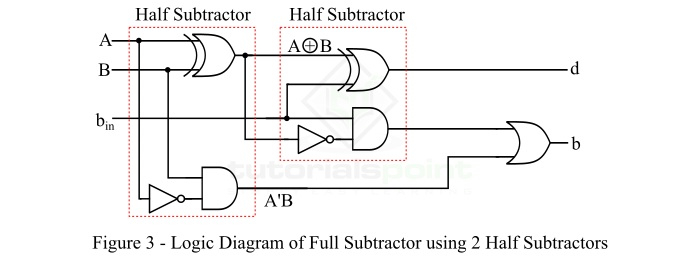

- Full Subtractor using 2 Half Subtractors

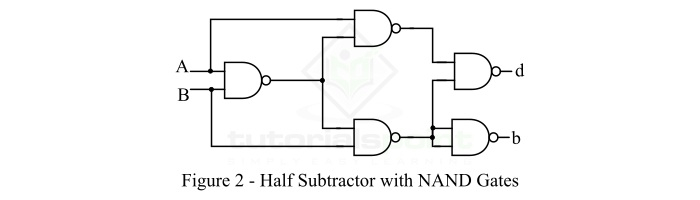

- Half Subtractor using NAND Gates

- Sequential Logic Circuits

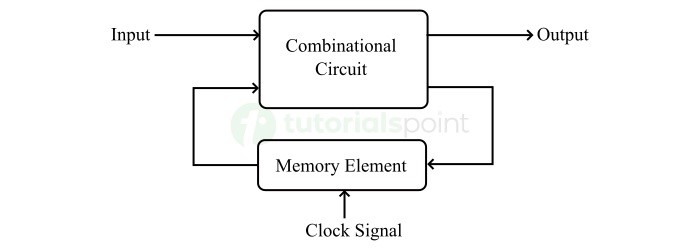

- Digital Sequential Circuits

- Clock Signal and Triggering

- Latches

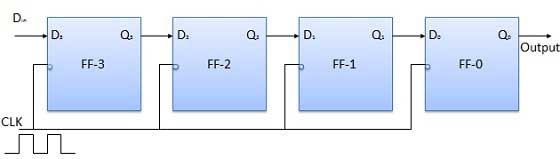

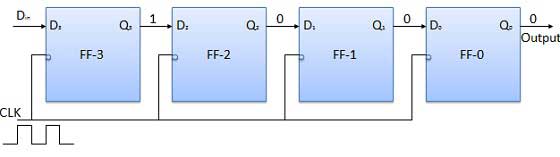

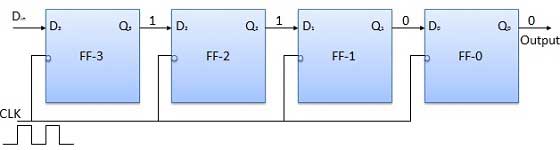

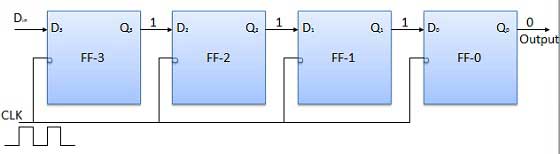

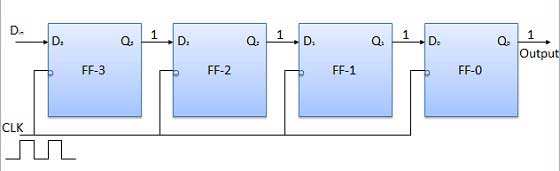

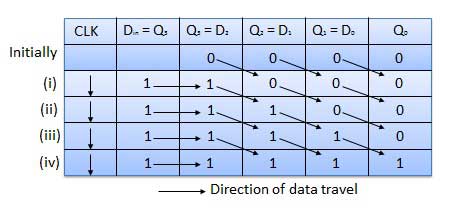

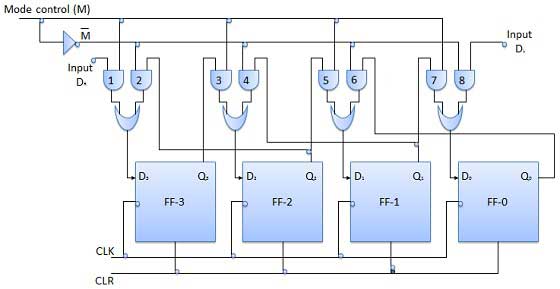

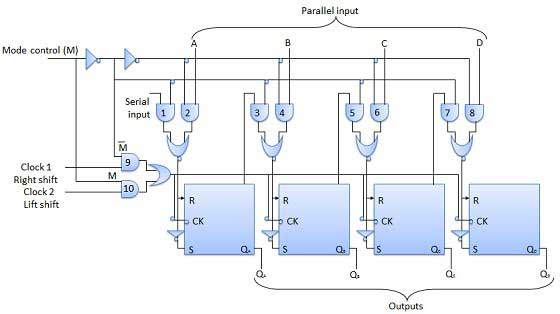

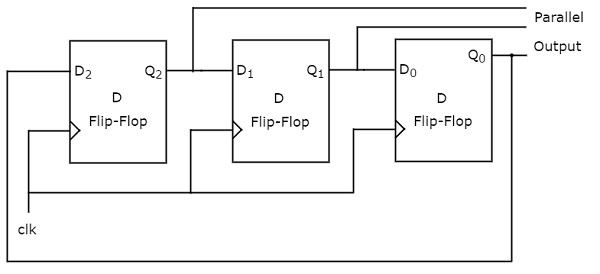

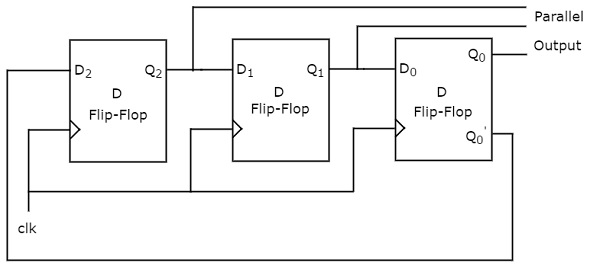

- Shift Registers

- Shift Register Applications

- Binary Registers

- Bidirectional Shift Register

- Counters

- Binary Counters

- Non-binary Counter

- Design of Synchronous Counter

- Synchronous vs Asynchronous Counter

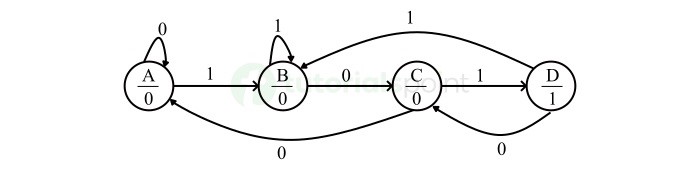

- Finite State Machines

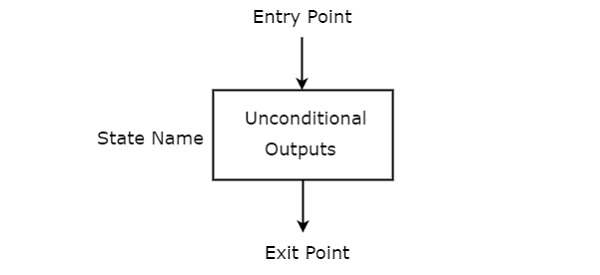

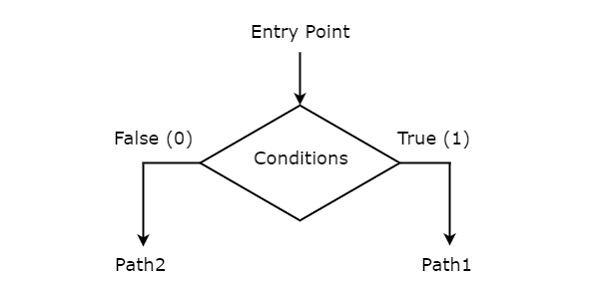

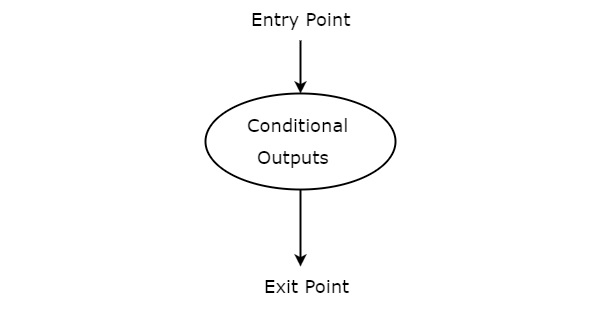

- Algorithmic State Machines

- Flip Flops

- Flip-Flops

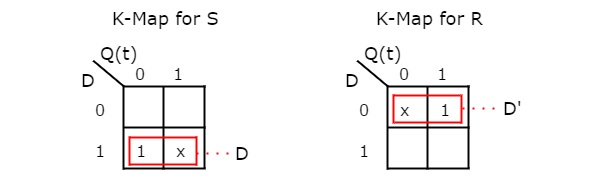

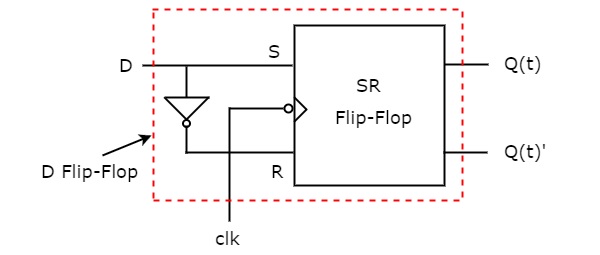

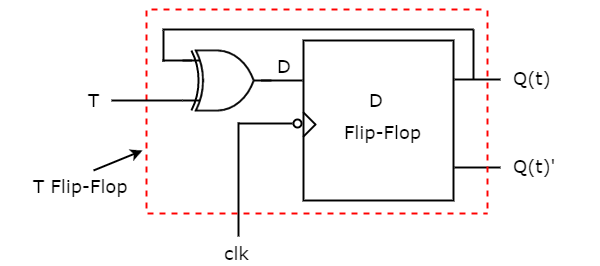

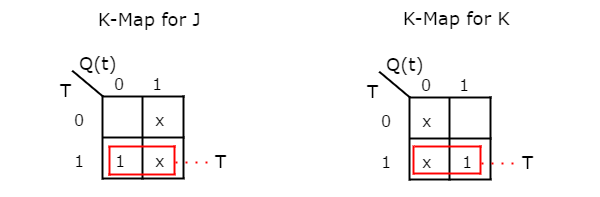

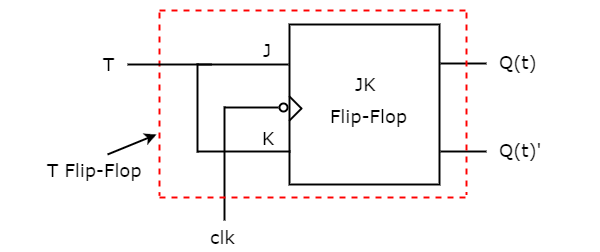

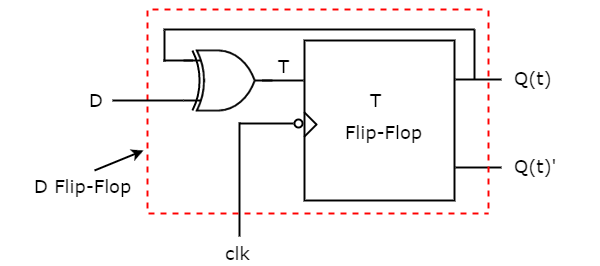

- Conversion of Flip-Flops

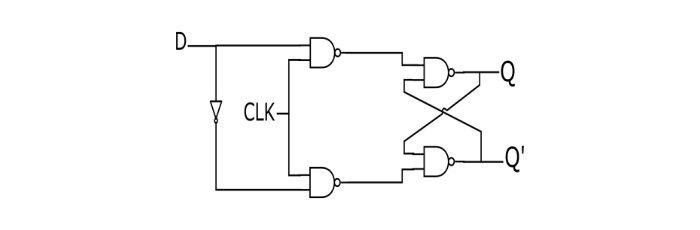

- D Flip-Flops

- JK Flip-Flops

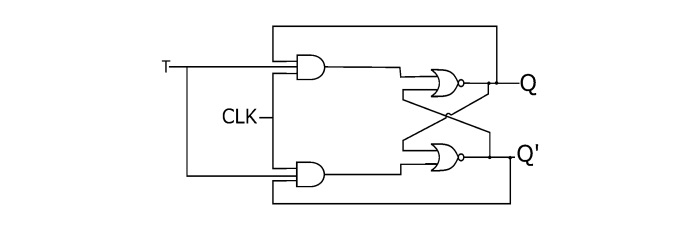

- T Flip-Flops

- SR Flip-Flops

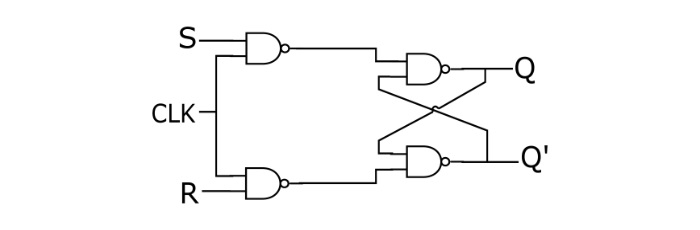

- Clocked SR Flip-Flop

- Unclocked SR Flip-Flop

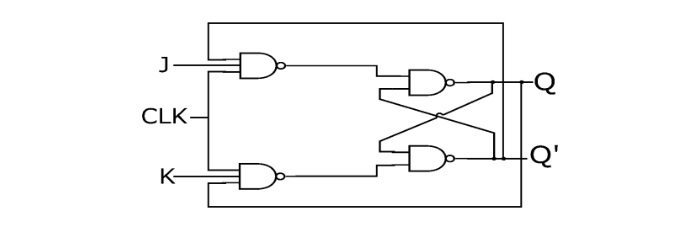

- Clocked JK Flip-Flop

- JK to T Flip-Flop

- SR to JK Flip-Flop

- Triggering Methods:Flip-Flop

- Edge-Triggered Flip-Flop

- Master-Slave JK Flip-Flop

- Race-around Condition

- A/D and D/A Converters

- Analog-to-Digital Converter

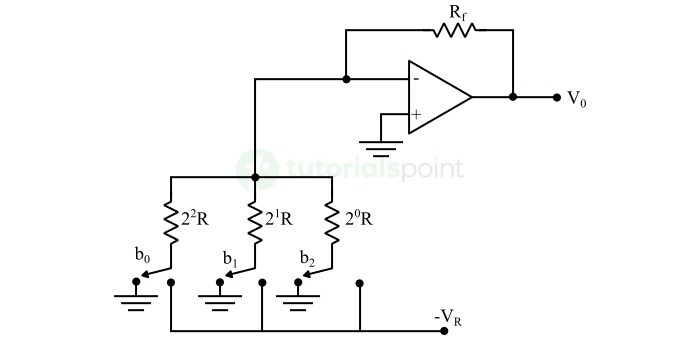

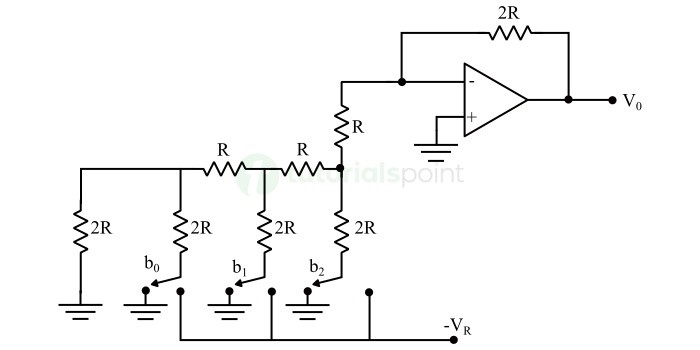

- Digital-to-Analog Converter

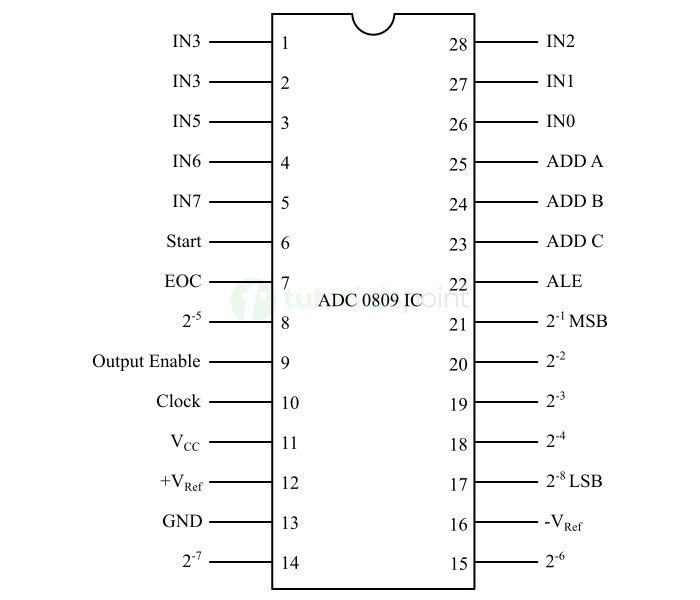

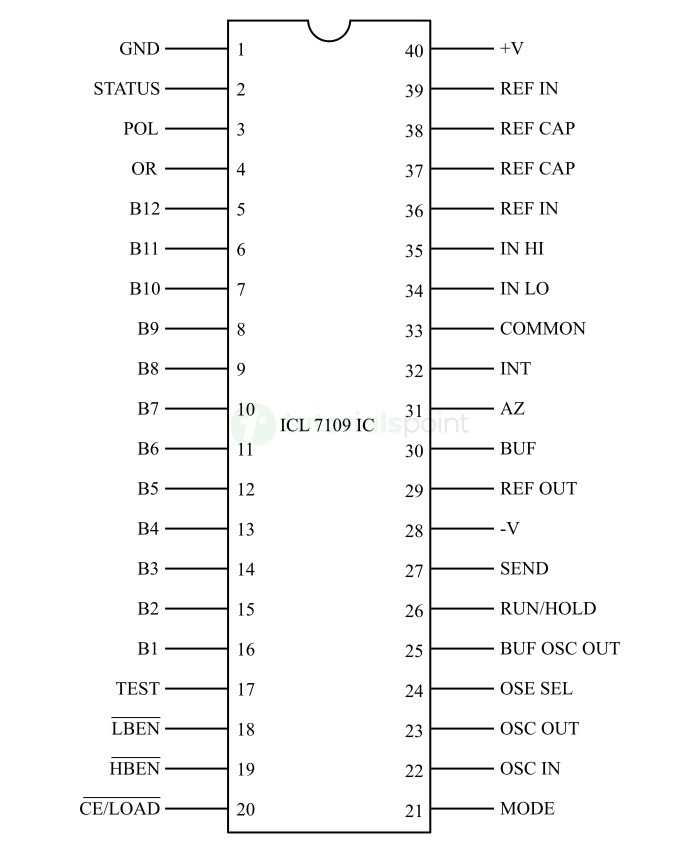

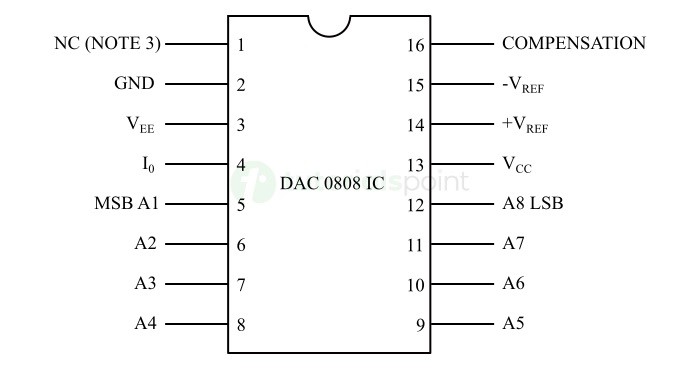

- DAC and ADC ICs

- Realization of Logic Gates

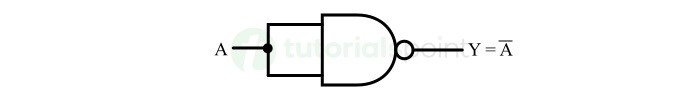

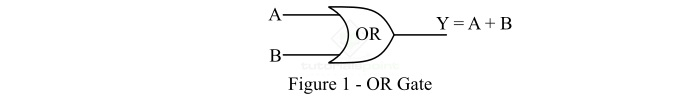

- NOT Gate from NAND Gate

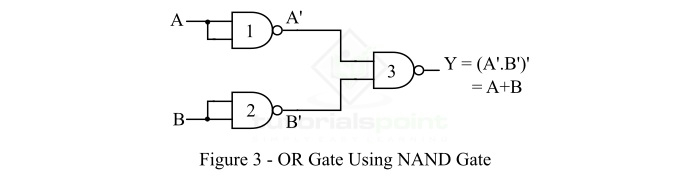

- OR Gate from NAND Gate

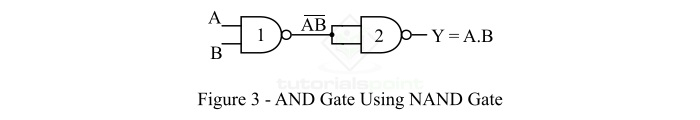

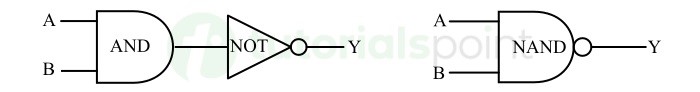

- AND Gate from NAND Gate

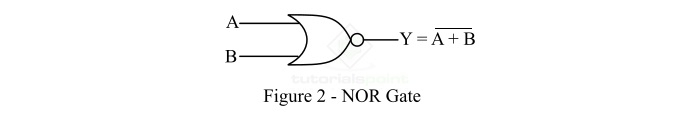

- NOR Gate from NAND Gate

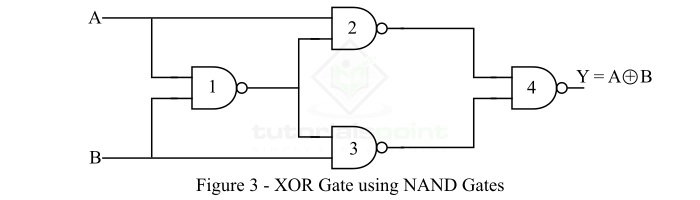

- XOR Gate from NAND Gate

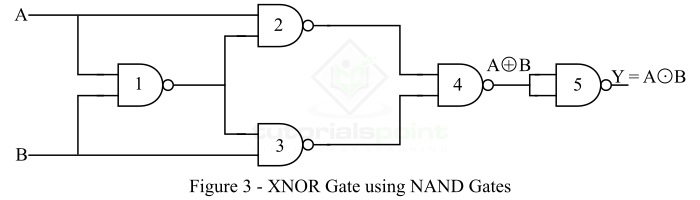

- XNOR Gate from NAND Gate

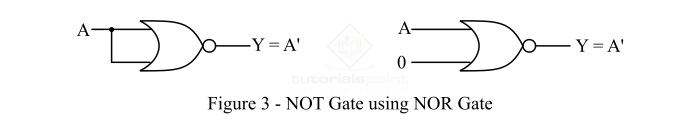

- NOT Gate from NOR Gate

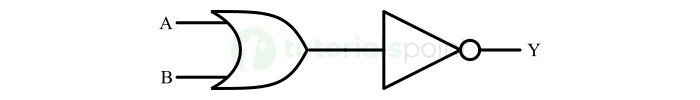

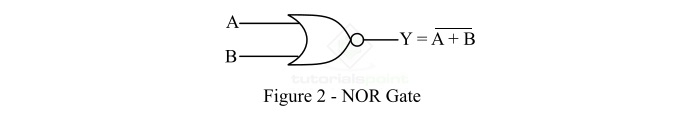

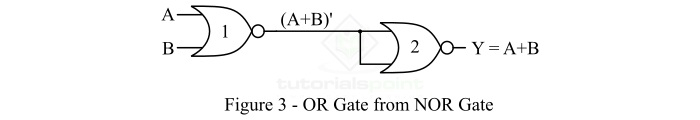

- OR Gate from NOR Gate

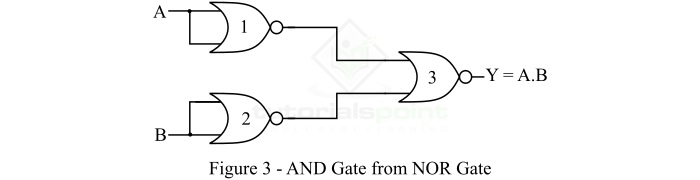

- AND Gate from NOR Gate

- NAND Gate from NOR Gate

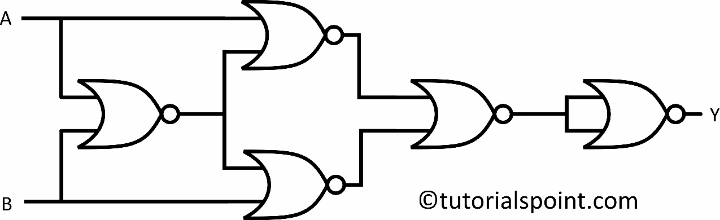

- XOR Gate from NOR Gate

- XNOR Gate from NOR Gate

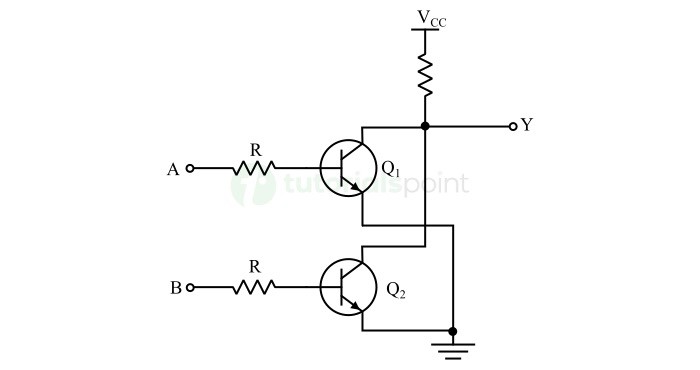

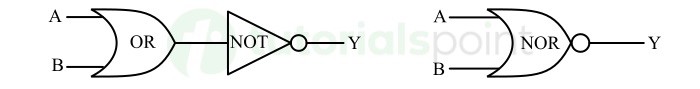

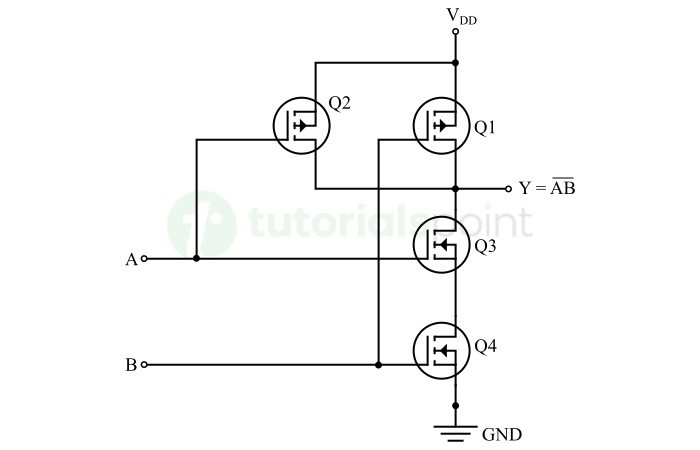

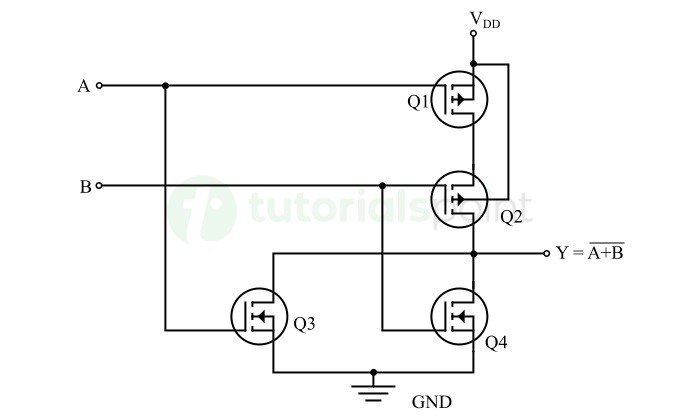

- NAND/NOR Gate using CMOS

- Full Subtractor using NAND Gate

- AND Gate Using 2:1 MUX

- OR Gate Using 2:1 MUX

- NOT Gate Using 2:1 MUX

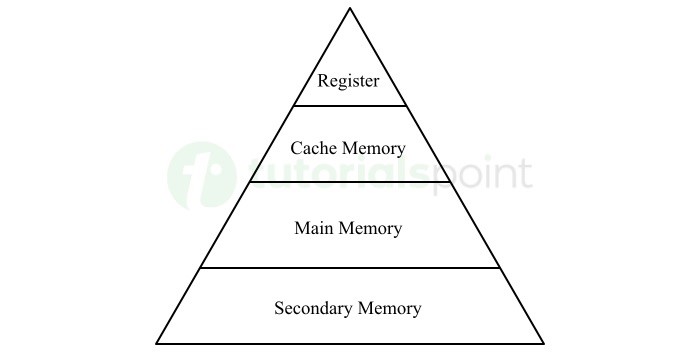

- Memory Devices

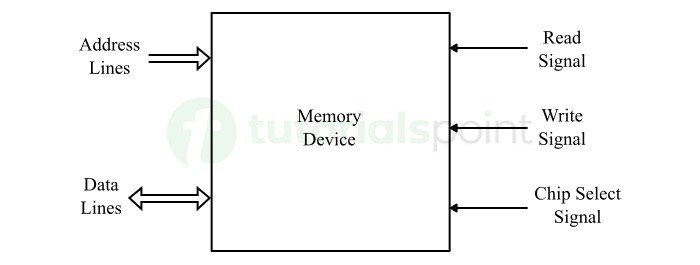

- Memory Devices

- RAM and ROM

- Cache Memory Design

- Programmable Logic Devices

- Programmable Logic Devices

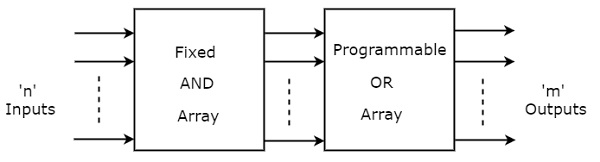

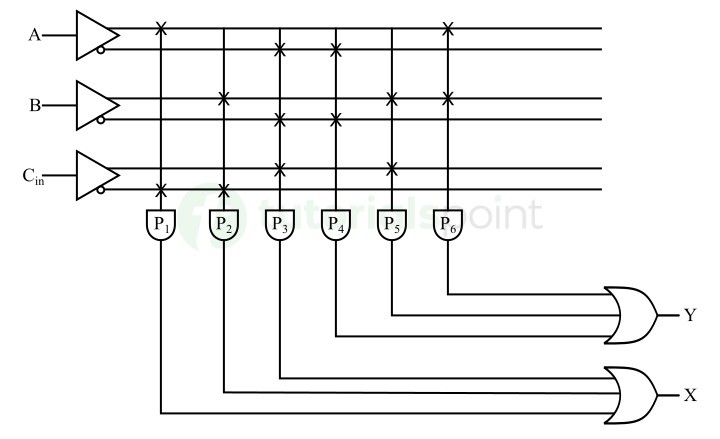

- Programmable Logic Array

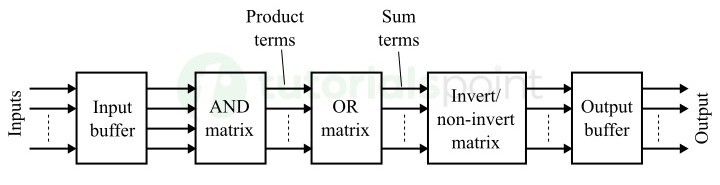

- Programmable Array Logic

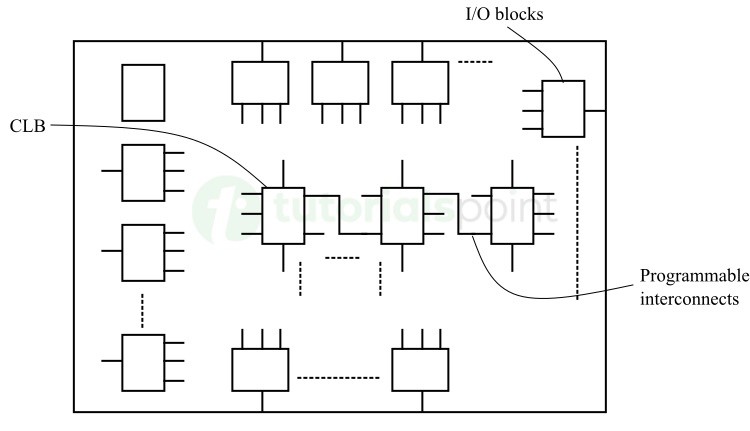

- Field Programmable Gate Arrays

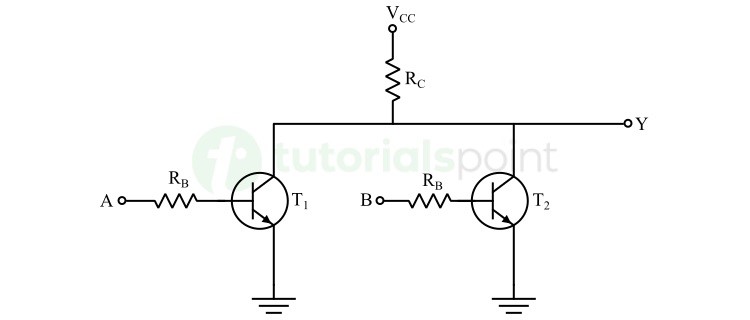

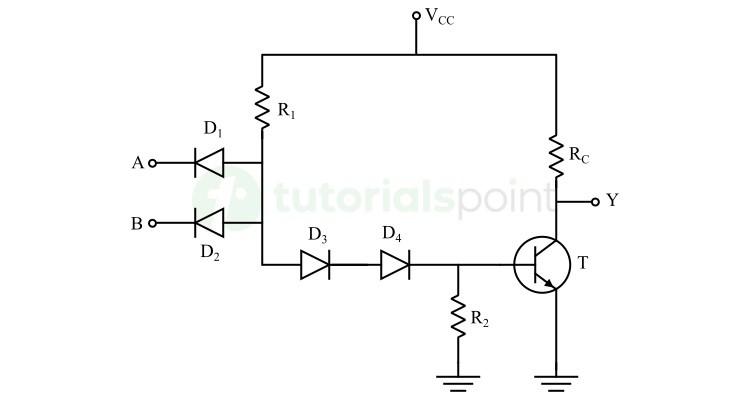

- Digital Electronics Families

- Digital Electronics Families

- CPU Architecture

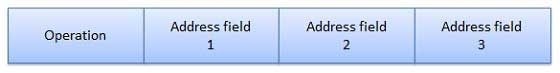

- CPU Architecture

- Digital Electronics Resources

- Digital Electronics - Quick Guide

- Digital Electronics - Resources

- Digital Electronics - Discussion

Digital Electronics - Quick Guide

Types of Digital Systems

A system is defined as a group of various components interconnected together to perform a specific task. For example, a digital computer consists of several components such as monitor, CPU (Central Processing Unit), memory, keyboard, mouse, printer, and more. All these components are connected together to accomplish certain tasks. Hence, a computer can be termed as a system.

We can broadly classify systems into the following two categories −

- Analog Systems

- Digital Systems

An analog system is a type of system that operates on continuous time signals, while a digital system is one that can work on discrete time signals.

Read this chapter to learn the basics of digital systems and their types.

What is a Digital System?

A type of electronic system that is designed to store, manipulate, and communicate digitally represented information is termed as a digital system. Some common examples of digital systems include smartphone, laptops, smartwatch, tablet, desktop computers, etc.

The working of a digital system is entirely based on digital signals or binary signals. Where, a digital signal is a type of signal that is represented as a discrete-elements. It can have two possible states namely high or low. The high state is denoted by the logic 1 and the low state is denoted by the logic 0.

In a digital system, if the state of the signal is logic 1, the system will be on, and if the state of the signal is 0, the system will be off.

Characteristics of Digital Systems

Today, digital systems are widely used in almost every aspect of life. This is because of their high reliability and efficiency. The following are some key characteristics of digital systems −

- Digital systems are relative less complex to implement as they use binary number system having only two digits to represent the state of a system.

- In digital systems, the information is represented in the form of a group of 0s and 1s i.e., bits. This is called binary or digital representation of information.

- Digital systems rely on digital signals having two well-defined discrete states. This makes digital systems more reliable and efficient in terms of processing, storage, and communication of information.

- Digital systems use logical mathematics and operations to perform computing tasks.

- Digital systems can be manufactured in the form of integrated circuits (ICs) of very small sizes.

- Digital systems can be easily programmed to perform repeated tasks that reduces human efforts and cost.

- Digital systems are highly immune to noise and distortions.

Types of Digital Systems

Digital systems can be classified based on various parameters. Here are some important types of digital systems that we commonly use in practice −

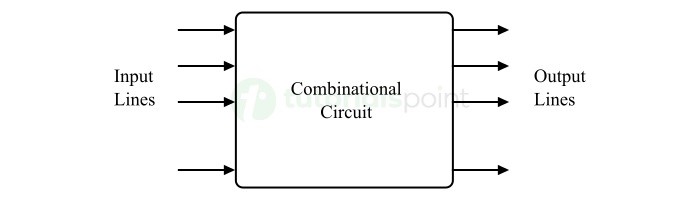

Combinational Digital Systems

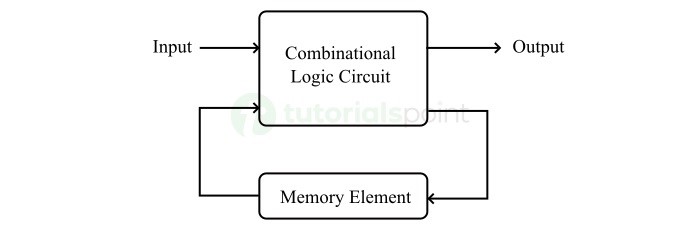

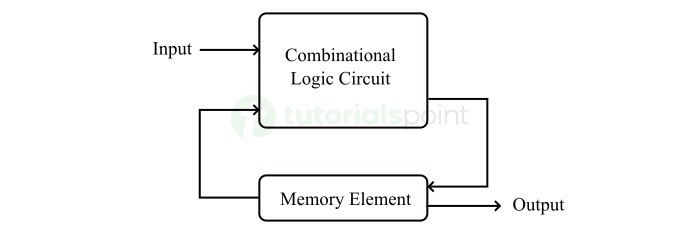

A combinational logic circuit or system is a type of digital circuit that performs logical operations and produces output depending on the present inputs. Hence, the output of a combinational digital circuit does not depend on the past inputs and outputs of the system.

Example − The common examples of combinational digital systems are binary adders, subtractors, logic gates, multiplexers, demultiplexers, etc.

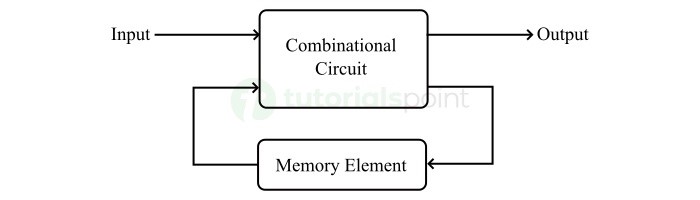

Sequential Digital Systems

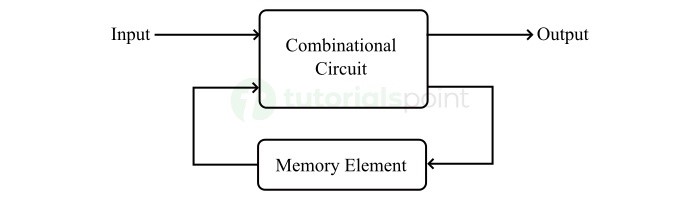

A type of digital system that has a memory element to store past history of the system operation is called a sequential digital system. Therefore, the output of a digital system depends on both present inputs and past outputs of the system.

Example of sequential digital systems are flip-flops, registers, memory devices, counters, etc.

Programmable Logic Devices (PLDs)

A programmable logic device is one that can be programmed to perform a specific task automatically.

Example of programmable logic devices are microcontrollers, PLCs, etc.

Digital Communication Systems

A digital communication system is a type of digital system used for transmission and reception of information in the form of digital signals.

Example of digital communication systems are internet, intranet, mobile communication system, Wi-Fi, etc.

Digital Control Systems

A digital control system is a computerized control system used to monitor and regulate the behavior of a dynamic system.

Example − Digital control systems are extensively used in robotics, industrial automation, etc.

Conclusion

In conclusion, digital systems are modern systems known for their high speed and reliability. A digital system utilizes digital signals to store, process, and communicate the information.

In this chapter, we explained the basics of digital systems and their types. Traverse to the next chapter to learn all about the types of signals used in the field of electronics engineering.

Types of Signals

In electronics engineering, an electrical quantity like voltage or current or electromagnetic wave that is used for transmission of data or information is called a signal.

Signals are considered the heart of any data communication or processing system like the Internet. Signals instruct the electronics hardware components to perform a certain task such as convey the information from one point to another.

Apart from voltage, current or electromagnetic signals, we also have optical signals, where the information is represented and transmitted in the form of light.

This chapter will explain the concept of signal and different types of signals used in electronics engineering.

What is a Signal?

A physical quantity that has capability to transmit information from one point to another is called a signal. Some common examples of signals include voltage, current, electromagnetic wave, optical signals, etc.

Signals are the backbone of any electronic processing or communication system. These can be transmitted through various types of communication channels like wires, space (electromagnetic waves), optical fibers, etc.

Properties of Signal

In electronics, a signal is characterized by the following important properties −

- Magnitude − The intensity or maximum value of a signal is termed as its magnitude.

- Frequency − The number of oscillations per second is called frequency of the signal.

- Time period − The time taken to complete one oscillation is called the time period of the signal.

Types of Signals

In electronics, there are mainly two types of signals used, they are −

- Analog Signals

- Digital Signals

Let us discuss these two types of signals in detail.

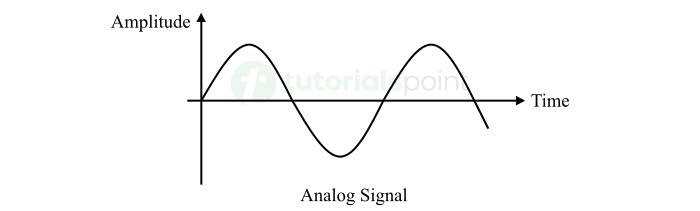

What is an Analog Signal?

A type of electronic signal that has continuous values within a given range is called an analog signal. Analog signals are expressed as the continuous functions of time. They are represented as the waveforms of continuously varying current or voltage.

Example of analog signals are voice, speed, pressure, temperature, etc.

An important characteristic of analog signals is that they have a definite value at every instant of time, known as instantaneous value of the signal.

Analog signals have smooth waveforms as they are continuous in both amplitude and time. That meant, there is no interruptions in their representation over time.

Properties of Analog Signal

The following are main properties of analog signals −

- Analog signals are continuous signals in both amplitude and time.

- Analog signals have a certain value or magnitude at any given instant of time.

- Analog signals have infinite resolution.

- Analog signals are best suited for representing the real-world phenomena.

- Analog signals are represented by the continuously varying smooth waveforms.

What is a Digital Signal?

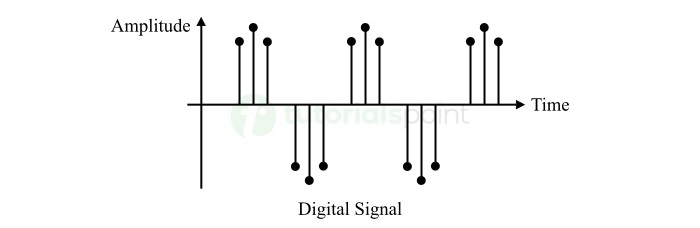

A digital signal is a type of electronic signal that has a finite set of discrete values representing information.

Digital signals are also called binary signals, as they use binary 0 or 1 to represent the state of a signal. Where, the binary 0 represents the off or low state of the signal, while the binary 1 represents the on or high state of the signal.

Thus, digital signals are expressed as discontinuous functions of time.

Properties of Digital Signal

The following are some key characteristics of digital signals −

- Digital signals have discrete or discontinuous values in terms of both amplitude and time.

- Digital signals do not have values defined between any two distinct instants of time.

- Digital signals are represented using binary system by sampling the values of the signals at specific time instants.

- Digital signals represent information in the form of a sequence of binary 0s and 1s.

- Digital signals have a finite resolution.

- Digital signals are capable to perform logical operations.

- Digital signals are more efficient and reliable when it comes to storage and transmission.

Difference between Analog and Digital Signals

Let us now discuss the important differences between analog and digital signals −

| Key | Analog Signals | Digital Signals |

|---|---|---|

| Representation | Analog signals are represented as continuous functions or waveforms of time. | Digital signals are represented as discrete functions of time. |

| Nature | Analog signals are continuous as they have infinite values within a specified range. | Digital signals are discontinuous as they have distinct values sampled at specific time instants. |

| Resolution | Analog signals have infinite resolution. | Digital signals have a finite resolution. |

| Accuracy | Analog signals are more accurate. | Digital signals are relatively less accurate. |

| Storage | Analog signals are difficult to store. | Digital signals are efficient to store. |

| Noise immunity | Analog signals are less immune to noise. | Digital signals have high immunity against noise. |

| Examples | Voice signals, temperature, speed, etc. | Data transmitted over internet, computer generated signals, etc. |

Applications of Signals

Both analog and digital signals are widely used in the field of electronics. The following are some key applications of signals −

- Signals are used for storage and transmission of information.

- Signals are used in control systems to regulate their behavior.

- Signals are also used in measurement of physical quantities like temperature, pressure, speed, sound, light, and more.

- Signals are used in computing systems for data processing, etc.

Conclusion

In electronics engineering, signals are most significant elements of a system. Signals are nothing but physical quantities like voltage, current, electromagnetic waves, light pulses, etc. used to convey information from one point to another.

In this chapter, we covered different types of signals and their properties. In the next chapter, we will cover the concept of logic levels and pulse waveform.

Logic Levels and Pulse Waveforms

A digital system is a type of electronic system that utilizes the binary number system to work. In other words, a digital system is a two-state electronic system used to represent two binary digits 0 and 1, where 0 represents the low or "off" state and 1 represents the high or "on" state of the system.

In the field of digital electronics, different voltage levels are used to represent the two binary values, i.e., 0 and 1 in a digital signal. These voltage levels are known as logic levels.

In this chapter, we will learn the concept of logic levels and pulse waveforms.

What is a Logic Level?

In digital electronics, a voltage level that represents a specific binary value either 0 or 1 is called a logic level. Here, the binary value 0 represents the low voltage level while the binary value 1 represents the high value level.

Hence, the logic levels can be classified into the following two types −

- High Logic Level

- Low Logic Level

Let’s discuss these two logic levels in detail.

High Logic Level

In the case of a digital system, the voltage level closer to the maximum voltage level that the system can handle without getting damaged is called high logic level.

The high logic level is represented by the binary digit "1". The voltage level for a high logic level depends on the technological standard used to design the system. Typically, the voltage value between 2 V and 5 V represents the high logic level or 1.

Low Logic Level

In a digital system, the low logic level is defined as the maximum voltage level for which the system will remain in the OFF state.

The low logic level is represented by the binary digit "0". Similar to the high logic level, the voltage level for a low logic level depends on the technology standard used to design the system. In actual practice, the voltage value between 0 V and 0.8 V represents the low logic level or logic 0.

In most practical digital system, the ground voltage is used to represent the low logic level.

Note − The voltage range between the voltage values 0.8 V and 2 V is known as the indeterminate logic range. If a digital signal lies between the value 0.8 and 2 V, the response of the system is not predictable.

What is a Pulse?

A pulse is a type of an electronic signal that can change suddenly between two possible states i.e., high state and low state.

The graph used to represent the transition of a pulse is called the pulse waveform. Pulses are very important in the operation of digital systems, communication systems, and many other electronics devices and circuits.

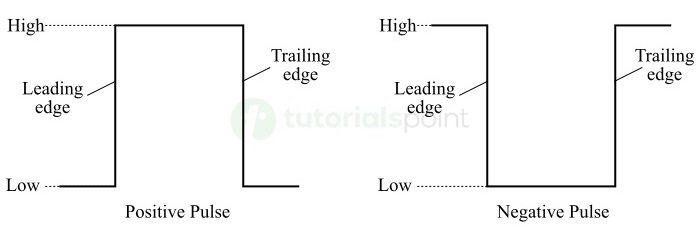

Depending on the switching characteristics, the pulses can be classified into the following two types −

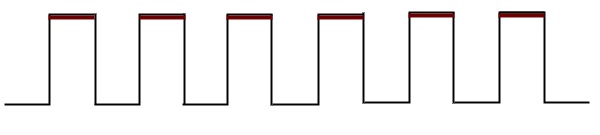

- Positive Pulse − When a signal normally goes from low logic level to the high logic level and then returns to its normal low logic level, then it is called a positive pulse.

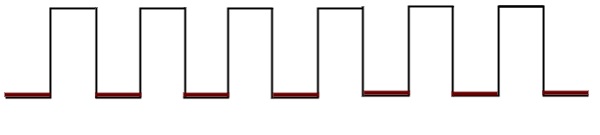

- Negative Pulse − When a signal normally goes from high logic level to the low logic level and then returns to its normal high logic level, then it is known as a negative pulse.

The pulse waveforms for positive and negative pulses are depicted in the following figure.

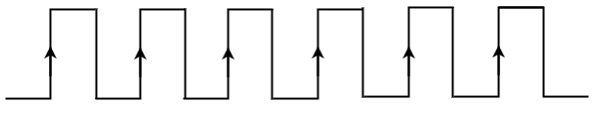

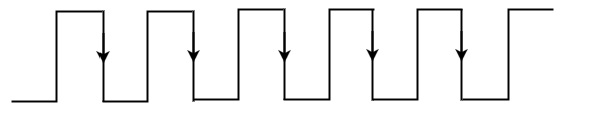

A pulse has two edges namely, a leading edge and a trailing edge.

In the case of a positive pulse, the edge going from low logic level to high logic level is called the leading edge, and the edge going from high logic level to low logic level is called the trailing edge.

In the case of a negative pulse, the edge going from high logic level to low logic level is called the leading edge, whereas the edge going from low logic level to high logic level is called the trailing edge.

The positive and negative pulse waveforms shown in the above figure are ideal pulse waveforms, because their leading and trailing edges change instantaneously i.e., in zero time. But in actual practice, the edges of pulses do not change instantaneously from low logic level to high logic level or from high logic level to low logic level.

The pulse waveforms that take a finite time to change from low logic level to high logic level and vice-versa are known as non-ideal pulse waveforms.

In the case of a non-ideal pulse waveform, the time taken by the pulse to go from low logic level to high logic level is called the rise time. The time taken by the pulse to go from the high logic level to the low logic level is called the fall time.

Types of Pulse Waveforms

The pulse waveforms used in digital systems are mainly classified into the following two types −

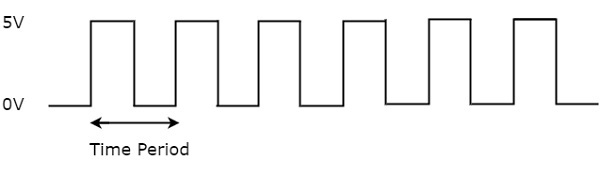

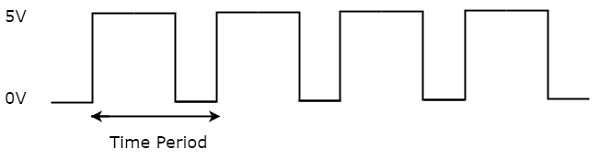

Periodic Waveforms

A pulse waveform that repeats itself at regular intervals of time is called a periodic waveform. The time taken to complete one cycle is called the time period of the periodic waveform.

Non-periodic Waveforms

A pulse waveform which does not repeat itself at regular intervals of time is termed as a non-periodic or aperiodic waveform.

Conclusion

In conclusion, "logic level" is a concept used in digital systems to represent the state of the system. There are two possible logic levels in the case of digital systems namely, high logic level and low logic level. The high logic level is represented by the binary 1 while the low logic level is represented by the binary 0.

The graphical representation of a digital signal or a pulse is termed as the "pulse waveform". Pulse waveforms are used to represent the transition of a pulse or digital signal or the states of a digital system. In this chapter, we have discussed the concept of logic levels and pulse waveforms. In the next chapter, we will learn about "components of a digital system".

Components of Digital System

A digital system is a type of electronic system used to store, process, and manipulate data represented in the form of digital signals, where a digital signal is a discrete time signal. Digital systems use binary number system to operate. Some common examples of digital systems include digital computers, laptops, smartphones, etc.

This chapter is meant for explaining the major components of a digital system.

Components of a Digital System

A typical digital system consists of the following main components −

- Central Processing Unit (CPU)

- Memory

- Input Devices

- Output Devices

- Logic Gates

- Power Supply

- Communication Channels

Let’s discuss each of these components of a digital system in detail.

Central Processing Unit (CPU)

In a digital system, the central processing unit is the most important component of the system, as it performs all the operations in the system. It is also known as processor.

The CPU is an electronic circuit that consists of two sub-circuits namely, arithmetic and logic unit, and control unit.

The arithmetic logic unit (ALU) is the part of a CPU that performs all the arithmetic and logical operations and executes the instructions to manipulate data. ALU is made up of logic gates and other electronic components. It can perform operations like addition, subtractions, comparison, etc.

The control unit (CU) is another major electronic circuit in the central processing unit that coordinate the operation of all other components of a digital system. It generates clock signals for the synchronization of the system.

Semiconductor Memory

Memory is another major component of a digital system. It is used to store and instructions in the system. In most digital system, semiconductor memory is used to store digital information.

Memory of a digital system can be classified into the following two types −

- Random Access Memory (RAM) − It is a temporary memory used to store data and instruction on which the CPU is currently working. Once the digital system is turned off, its data will be deleted.

- Read Only Memory (ROM) − ROM is also an important component of a digital system. It is a permanent memory used to store those data and instructions that require again and again to perform tasks.

In digital systems, both RAM and ROM are used in the form of ICs made up of semiconductors.

Apart from RAM and ROM, digital systems may also support external memory devices like CD, DVD, Pen Drive, SD card, etc. All these external memories are used for permanent data storage.

Input Devices

Input devices are those electronic components of a digital system used for entering data into the system. Examples of input devices include keyboard, mouse, scanner, sensors, camera, light pen, code readers, etc.

Input devices are designed to accept data in the form of a specific type or format and convert them into digital signals for processing.

For example, a keyboard gets outside instructions in the form of keystrokes and then convert them into digital signals.

Output Devices

Output devices are those components of a digital system that allow users to view the processed data or information. Examples of output devices are monitor, display screens, printers, projectors, speakers, etc.

Output devices are designed to accept digital signals and convert them in a suitable format to make them readable by human.

For example, a monitor takes digital signals and convert them as visuals and display on a screen.

Logic Gates

Logic gates are essential components of any digital system. They are the fundamental building block of the digital system. Logic gates are nothing but electronic circuits that can perform logical operations.

In digital systems, logic gates are used to realize all the information processing and storage systems. The most commonly used logic gates are AND, OR, NOT, NAND, NOR, Ex-OR, and Ex-NOR.

Power Supply

Power supply is the energy bank of the digital system that provides necessary electric power to the components of the system so they can work.

The primary function of the power supply unit of a digital system is to convert the electric power received from an external source into the desired type and voltage level required by the system.

Most digital systems work on 5 V DC supply. Hence, the power supply unit receives 220 V AC from the supply mains and convert it to 5 V DC supply. Also, the power supply unit regulates the fluctuations occurring in the power supply to protect the system from damages.

Communication Channels

In a digital system, the communication channel is also known as bus system. It consists of several different types of buses (conductors) such as data bus, address bus, and control bus. These communication channels allow data transmission between different components of the system.

Conclusion

In conclusion, a digital system consists of several components. Some important components of a typical digital system are described in this chapter. All these components are connected together and allowed to communicate to perform different jobs. In the next chapter, we will learn about different types of "digital logic operations".

Digital Logic Operations

In the field of digital electronics, many digital logic operations are performed which are considered as the fundamental building blocks. All the digital logic operations are based on the binary number system and Boolean algebra, where the data and information are represented in the form of binary 0s and 1s. Digital logic operations are used to manipulate the binary digits to perform various tasks.

In this chapter, we will learn about commonly used digital logic operations in the field of digital electronics. Here are some widely used digital logic operations −

- Arithmetic Operations

- Logical Operations

- Encoding and Decoding

- Multiplexing and Demultiplexing

- Code Conversion

- Comparison

- Counting

- Data Storage

- Data Transmission

Let’s discuss each of these digital logic operations in detail along with their applications.

Arithmetic Operations in Digital Electronics

Arithmetic operations are basic mathematical operations like addition, subtraction, multiplication, division, etc. In digital electronics, these arithmetic operations are performed using various digital circuits like adders, subtractors, multiplier, etc.

In digital electronic systems, the given numbers are first converted into binary format and then desired operations are performed on them.

Arithmetic operations are one of the fundamental operations performed using various digital electronic systems like microprocessors, calculators, microcontrollers, etc.

The following are the four main arithmetic operations performed by a digital system −

Addition

Addition is performed by using a digital logic circuit called adder. It adds two numbers and generates a sum and a carry as output. For example, if 8 and 5 are two numbers, then adder will produce a sum term 3 and a carry output 1.

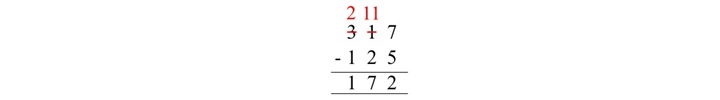

Subtraction

The arithmetic operation subtraction is performed by using a digital logic circuit called subtractor. It performs the subtraction of two numbers and produces a difference term and a borrow term as output.

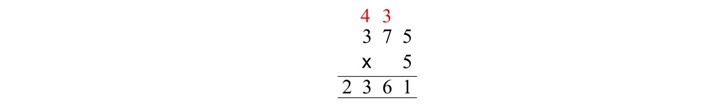

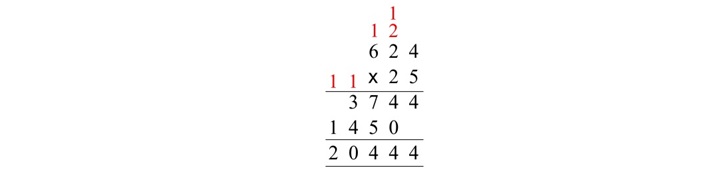

Multiplication

A digital circuit used to perform multiplication of two numbers is called a multiplier. It multiplies the given numbers and generates a product term as output.

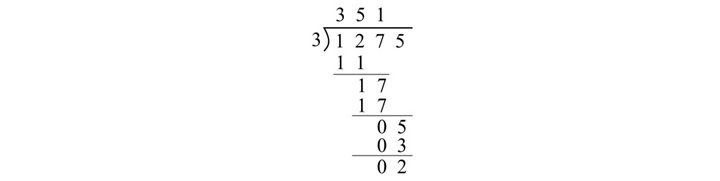

Division

The division operation of two numbers is performed by using a digital circuit called divider. It performs division of two numbers and generates a quotient term and remainder term as output.

Logical Operations in Digital Electronics

Logical operations are used to compare two input parameters to make a decision. The commonly used logical operations in digital systems are OR, AND, NOT, NAND, NOR, XOR, and XNOR. All these logical operations are used to manipulate binary data to make crucial decisions in a digital system.

Logical operations are widely used for developing algorithms and conditional statements in programming.

Here are the commonly used logical operations in digital electronics −

AND

It is a basic logic operation performed by using a digital circuit called AND gate. In the AND operation, the output is true only if all of the inputs are true.

OR

OR is another basic logic operation in digital electronics. It is performed by using a digital logic circuit called OR gate. It produces a true output if any of the inputs are true.

NOT

NOT is a digital logic operation performed by using a circuit called NOT gate or inverter. It is also known as inversion operation. It generates a complement of the input.

NAND

NAND is a combination of AND and NOT operation. It is performed by using a digital circuit called NAND gate. The output of the NAND gate is false only if all of the inputs are true.

NOR

This logical operation is a combination of OR and NOT operations. It is performed by using a digital circuit called NOR gate. In the case of NOR operation, the output is false if any of the inputs are true.

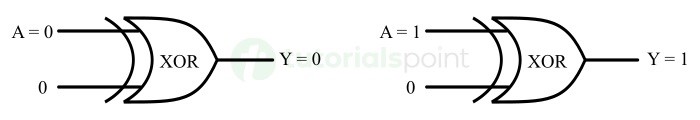

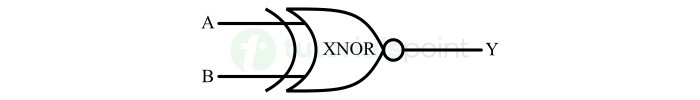

XOR

The logical operation XOR or Exclusive OR is performed by using a digital logic circuit called XOR gate. In the case of XOR operation, the output is true if the number of true inputs is odd.

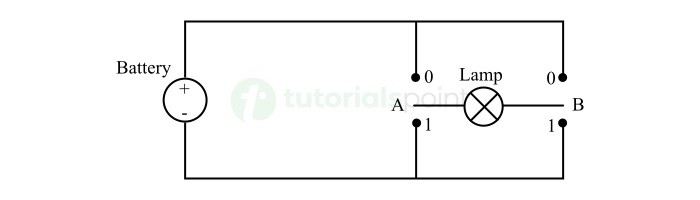

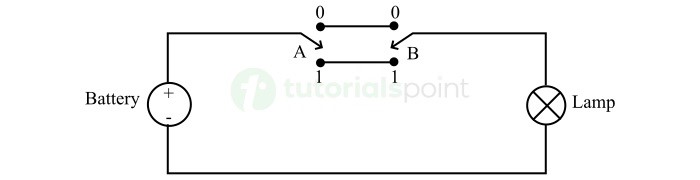

XNOR

The logical operation XNOR is a combination of XOR and NOT operations. It is performed by using a digital logic circuit called XNOR gate. In the case of XNOR gate, the output is true if all of the inputs are either true or false.

Encoding and Decoding in Digital Electronics

In digital electronics, encoding is a digital logic operation used to convert a familiar number or symbol into a coded format. A digital circuit called encoder is used to perform encoding, where the encoder receives digits, alphabets, and symbols and converts them into their respective binary codes.

On the other hand, decoding is the inverse operation of encoding. It is performed by using a digital logic circuit called decoder. Decoding is a digital logic operation that involves the conversion of a binary-coded information to other format like decimal, octal, hexadecimal, alphabets or symbols.

Both encoding and decoding are used in digital communication, error correction, data compression, etc.

Multiplexing and Demultiplexing in Digital Electronics

Multiplexing is a digital logic operation that combines multiple signals into a single signal. Hence, it is also termed as data sharing or selecting. A digital circuit called multiplexer is used to perform multiplexing. Multiplexing involves the process of switching information from multiple input lines on to a single output line in a specific sequence.

Demultiplexing is the reverse process of multiplexing. In the case of demultiplexing, information is switched from one input line on to multiple output lines. The digital circuit used to perform demultiplexing is called a demultiplexer.

Multiplexing and demultiplexing are two widely used digital logic operation in optimization of communication channels.

Code Conversion in Digital Electronics

Code conversion is a digital logic operation that involves converting information coded in one form to another form. It is performed by using a digital circuit called code converter.

Code conversion is an essential operation in interfacing between different digital systems. Some common examples of code converters are BCD to XS-3 converter, XS-3 to gray converter, etc.

Comparison Operation in Digital Electronics

Comparison is a digital logic operation performed using a digital circuit called comparator. The comparator compares two quantities and generates an output signal indicating whether the two input quantities are equal or not.

Counting Operation in Digital Electronics

Counting is a digital logic operation performed by using a digital circuit called counter. It involves the counting of increase or decrease in binary numbers.

Counting operation plays a vital role in various digital devices like memory, timers, digital clocks, microprocessors, etc. It is used to control the sequence of operation in a digital system.

Data Storage in Digital Electronics

Data storage is an essential operation in digital systems. It involves storing and retrieving digital data and information stored in the memory devices. Data storage can be performed using various digital storage devices like flip-flops, registers, memory units, etc.

Data Transmission in Digital Electronics

Data transmission is a digital logic operation in which binary data is transferred from one point to another in a digital system. In digital electronics, data transmission can be done either through wires or wireless channels.

Data transmission is a fundamental operation in digital communication where data is exchanged between different components of the system.

Conclusion

In conclusion, digital logic operations are used to manipulate binary data to perform various operations. They are considered as the fundamental building blocks of digital systems like microprocessors, microcontrollers, memory devices, communication systems, etc. Hence, it is essential to understand the digital logic operations for designing reliable digital systems and understand their behavior.

In this chapter, we covered all the essential digital logic operations along with their applications. In the next chapter, we will learn the advantages and limitations of digital systems.

Advantages and Limitations of Digital Systems

A digital system is an interconnected group of components that can process, store, and transmit digital data i.e., data represented in the form of binary codes. Digital signals are represented using binary values, 0s and 1s. A digital system can understand and manipulate data and information represented in the form of 0s and 1s.

Digital systems are implemented using highly reliable and efficient electronics components like logic gates and integrated circuits (ICs). They are known for their high speed and reliability.

Digital systems are extensively used in various fields like communication, computing, control system, data processing, etc.

Examples of digital systems are computers, smartphones, tablets, telecommunication networks, etc. Today, digital systems form an essential part of our modern technological world. In this chapter, let's focus on the advantages and disadvantages of digital systems.

Advantages of Digital Systems

Digital systems offer several advantages over analog systems. Some of the important advantages of digital systems are explained below −

Easy to Design

As we know, digital systems are two state switching circuits that have only two voltage levels namely, HIGH and LOW. Hence, it is easier to design a digital system.

In the case of digital systems, the knowledge of intermediate values of voltages are not important, but the lower and upper limits in which they fall are important. Therefore, digital circuits are less complex to design and implement.

Easy Information Storage

In digital systems, data and information are represented in the form of binary digits, i.e., 0s and 1s. There are several types of magnetic, optical, and semiconductor memories available to store digital data.

It is very easy to store digital information in a digital storage device like pen drive that provides a compact and efficient method to store data for long periods as compared to analog storage devices.

High Accuracy and Precision

Digital systems have higher accuracy and precision as compared to analog systems. This is because, it is very easy to expand a digital system to handle more binary digits just by adding more digital circuits to the system.

Also, digital systems are highly immune to interference. Hence, they can process, store, and transmit data without loss of accuracy.

Flexibility in Programming and Versatility

The operation of a digital system can be controlled by writing a set of instructions called program. We can easily reprogram the system to change its operation without changing its hardware configuration. Hence, digital systems are more versatile than analog systems.

High Noise Immunity

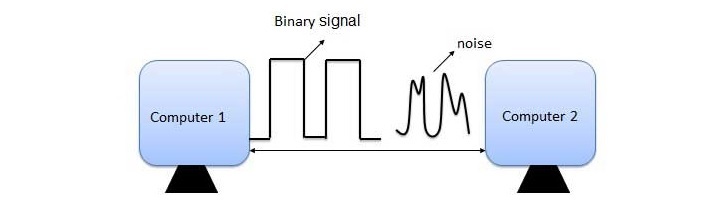

In digital electronics, unwanted electronic signals are called noise. The electronic noise can disturb the normal operation of a system. Digital systems can have various error checking and correction mechanisms that make them more immune to noise and interference over analog systems.

High Reliability and Durability

Digital systems use components that are less susceptible to variations and aging. This characteristic makes the digital systems more reliable and durable as compared to analog systems. Hence, digital systems can be used with consistent performance for long periods.

Easy Fabrication on IC Chips

The fabrication of digital integrated circuits is simple and less costly as compared to analog ICs. Also, higher degree of integration can be achieved in the case of digital ICs, as the digital ICs do not require high value capacitors, precision resistors, and inductors.

High Security

Digital systems are highly secure than analog systems, as we can implement various advanced security and encryption technologies to protect sensitive information stored in the system.

All these are the major benefits of digital systems that make them suitable for various applications like computing, telecommunication, automation, robotics, and more.

However, digital systems also have certain limitations over analog systems. Let’s discuss these limitations of digital systems in the following section.

Limitations of Digital Systems

Digital systems have numerous advantages, but they can also have some limitations that play a vital role in their designing and applications. The following are some key limitations of digital systems −

Need of Analog to Digital Conversion

In the real world, most physical quantities are analog in nature. Hence, before processing using a digital system, we need to convert these analog quantities into digital form. At the end of processing, the results are also converted back to the analog form.

Increased Complexity and Cost

As the digital systems require analog to digital and digital to analog converter and complex algorithms to perform operations. These practices increase complexity and cost of designing of the system.

Slow Processing Speed

Although digital systems have fast speeds, they cannot be used in some real-time applications due to need of extremely high processing speed. Under such situations, analog systems are more suitable over digital systems.

Sampling Rate Limitations

Real-world signals are analog, hence, proper sampling is important while converting them into digital signals. If the sampling rate is not chosen correctly, it can result in the loss of information in the digital system. Hence, digital systems are also subjected to a limitation in sampling rate.

Voltage Level Limitations

As digital systems use binary volage levels i.e., HIGH and LOW voltages. Therefore, they are limited in a certain range of voltage levels. Due to this reason, digital systems cannot be used in applications where a continuous range of voltages is required.

Conclusion

Digital systems have several advantages that make them suitable to use in modern technological applications. Due to high reliability, ease of integration, high security, etc. digital systems are being widely used in various fields like telecommunication, medical, science, research, etc.

Electronics engineers and designers are continuously working to optimize the digital systems to increase their performance and area of applications.

Digital systems however have some limitations like finite resolution, limited voltage levels and sampling rates, relatively slow speed, etc. These limitations have to be addressed while designing and implementation for better advancement in digital technologies.

Digital Electronics - Number Systems

A digital number system is a positional number system that has some symbols called digits. It provides a complete set of digits, operators, and rules to perform operations.

In a digital number system, the number of digits used determines the base of the number system. For example, the binary number system has two digits (0 and 1), hence, the base of the binary number system is 2.

Digital number systems form the foundation of the modern computing technologies and digital electronics. They are used to represent, process, and manipulate the information using a digital system.

In this chapter, we will discuss the fundamental concepts of different types of digital number systems.

Types of Digital Number Systems

In digital electronics, the following four types of digital number systems are mainly used −

- Binary Number System

- Decimal Number System

- Octal Number System

- Hexadecimal Number System

Let’s discuss each of these number systems in detail.

Binary Number System

Binary number system is the fundamental building block behind the implementation and working of all digital systems.

Binary number system has two symbols or digits, i.e., 0 and 1. Hence, these two digits are used to represent information and perform all the digital operations. Each binary digit is called a bit.

Since there are two digits are used in the binary number system, hence its base is 2. Therefore, the value of a binary number is calculated as the sum of powers of 2.

Binary digits are used in digital system to represent their ON and OFF states. Where, 0 is used to represent the OFF state of the digital system and 1 is used to represent the ON state of the system.

Overall, the binary number system forms the foundation of computation, digital communication, and digital information storage.

Example

Consider the binary number 1101.011. The integer part of this number is 1101 and the fractional part of this number is 0.011. The digits 1, 0, 1 and 1 of the integer part have weights of 20, 21, 22, 23 respectively. Similarly, the digits 0, 1 and 1 of fractional part have weights of 2-1, 2-2, 2-3 respectively.

Mathematically, we can write it as,

$$\mathrm{1101.011 \: = \: (1 \: \times \: 2^{3}) \: + \:(1 \: \times \: 2^{2}) \: + \: (0 \: \times \: 2^{1}) \: + \: (1 \: \times \: 2^{0}) \: + \: (0 \: \times \: 2^{−1}) \: + \: (1 \: \times \: 2^{−2}) \: + \: (1 \: \times \: 2^{−3})}$$

After simplifying the right-hand side terms, we will get a decimal number, which is an equivalent of binary number on left-hand side.

Decimal Number System

Decimal number system is not inherently a digital number system. But it is widely used to represent the digital information in a human readable format.

Decimal number system is a base 10 number system having 10 unique digits i.e., 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. It is the standard number system used by human beings to represent information in a natural way. However, a digital system cannot directly process the information represented in decimal form, so it is converted into binary form and then processed.

The base of the decimal number system is 10. So, the value of a decimal number is calculated by the sum of powers of 10.

Example

Consider the decimal number 1358.246. The integer part of this number is 1358 and the fractional part of this number is 0.246. The digits 8, 5, 3 and 1 have weights of (10)0, (10)1, (10)2 and (10)3 respectively. Similarly, the digits 2, 4 and 6 have weights of (10)-1, (10)-2 and (10)-3 respectively.

Mathematically, we can write it as,

$$\mathrm{1358.246 \: = \: (1 \: \times \: 10^{3}) \: + \:(3 \: \times \: 10^{2}) \: + \: (5 \: \times \: 10^{1}) \: + \: (8 \: \times \: 10^{0}) \: + \: (2 \: \times \: 10^{−1}) \: + \: (4 \: \times \: 10^{−2}) \: + \: (6 \: \times \: 10^{−3})}$$

After simplifying the right-hand side terms, we will get the decimal number, which is on the left-hand side.

Octal Number System

The octal number system is another type of digital number system used in the field of digital electronics to represent information. It is a base 8 number system having eight unique digits i.e., 0, 1, 2, 3, 4, 5, 6, and 7.

It is important note that the octal number system is equivalent to 3-bit binary number system as 23 = 8. Hence, this number system can be used in computing and digital electronic applications.

The value of an octal number is obtained by the sum of powers of 8, as 8 is the base of the octal number system.

Octal number system is used in the field of digital electronics to represent binary information in compact form, permissions in Linux or Unix systems, IPv6 address, binary machine code instructions, in error detection algorithms, etc.

Example

Consider the octal number 1457.236. Integer part of this number is 1457 and fractional part of this number is 0.236. The digits 7, 5, 4 and 1 have weights of (8)0, (8)1, (8)2 and (8)3 respectively. Similarly, the digits 2, 3 and 6 have weights of (8)-1, (8)-2, (8)-3 respectively.

Mathematically, we can write it as,

$$\mathrm{1457.236 \: = \: (1 \: \times \: 8^{3}) \: + \:(4 \: \times \: 8^{2}) \: + \: (5 \: \times \: 8^{1}) \: + \: (7 \: \times \: 8^{0}) \: + \: (2 \: \times \: 8^{−1}) \: + \: (3 \: \times \: 8^{−2}) \: + \: (6 \: \times \: 8^{−3})}$$

After simplifying the right-hand side terms, we will get a decimal number, which is an equivalent of octal number on the left-hand side.

Hexadecimal Number System

The hexadecimal number system is a base 16 number system. It has 16 digits, 0 to 9 and A to F. Where, A represents 10, B represents 11, C represents 12, D represents 13, E represents 14, and F represents 15. The hexadecimal number system is equivalent to a 4-bit binary number system as 24 = 16. Thus, the value of a hexadecimal number can be calculated by the sum of powers of 16.

In the field of digital electronics, the hexadecimal number system is used in memory address representation, digital colors representation, low level computer programming, encoding, assembly language programming, microcontrollers, keyboards, etc. Hexadecimal number system creates a balance between digital representation and human readability.

Example

Consider the hexadecimal number 1A05.2C4. The integer part of this number is 1A05 and the fractional part of this number is 0.2C4. The digits 5, 0, A and 1 have weights of (16)0, (16)1, (16)2 and (16)3 respectively. Similarly, the digits 2, C and 4 have weights of (16)-1 , (16)-2 and (16)-3 respectively.

Mathematically, we can write it as,

$$\mathrm{1A05.2C4 \: = \: (1 \: \times \: 16^{3}) \: + \:(10 \: \times \: 16^{2}) \: + \: (0 \: \times \: 16^{1}) \: + \: (5 \: \times \: 16^{0}) \: + \: (2 \: \times \: 16^{−1}) \: + \: (12 \: \times \: 16^{−2}) \: + \: (4 \: \times \: 16^{−3})}$$

After simplifying the right-hand side terms, we will get a decimal number, which is an equivalent of the hexadecimal number on the left-hand side.

Advantages of Digital Number Systems

The following are some key advantages of digital number systems −

- Digital number systems provide a simple and consistent way of representing and understanding information.

- Digital number systems allow to develop efficient methods for storage and transmission of digital information.

- Digital number systems provide methods of representing different types of information like text, numbers, images, etc.

- Digital number systems allow to convert information from one form to full fill the needs of applications.

- Digital number systems create compatibility between hardware and software.

Applications of Digital Number Systems

Digital number systems are used in various digital electronic fields such as computing, internet, communication, signal processing, and more. Here are a few examples of applications of digital number systems −

- Information Representation

- Digital Communication

- Storage and Transmission of Digital Data and Information

- Algorithm Development

- System Programming, etc.

Conclusion

In this chapter, we discussed the basic concepts of digital number systems. The understanding of digital number systems is essential for designing, implementing, and troubleshooting the digital systems. Digital number systems provide different methods of representing and manipulating information in digital systems.

Digital Electronics - Base Conversions

In the previous chapter, we explained the different types of number systems used in digital electronics. In this chapter, we will explain how you can convert a number from one base to another.

What is Number System Conversion?

Number system conversion is a process of converting a number from one base to another. Number system conversion is an important concept to represent information in different forms. In digital electronics, the following number system conversions are mostly performed.

- Binary to Decimal Conversion

- Decimal to Binary Conversion

- Binary to Octal Conversion

- Octal to Binary Conversion

- Octal to Decimal Conversion

- Decimal to Octal Conversion

- Hexadecimal to Binary Conversion

- Binary to Hexadecimal Conversion

- Hexadecimal to Decimal Conversion

- Decimal to Hexadecimal Conversion

- Octal to Hexadecimal Conversion

- Hexadecimal to Octal Conversion

Let us understand each of these number system conversions with the help of examples.

Binary to Decimal Conversion

We can convert a binary number into its equivalent decimal number by using the positional weights method.

In this method of binary to decimal conversion, each digit of the given binary number is multiplied by its positional weight. Then, all the products are added to obtain the equivalent decimal number.

The step-by-step process of converting a binary number to its equivalent decimal number by using positional weights method is explained below −

Step 1 − Write the positional weights for each binary digit.

Step 2 − Multiply each binary digit with its positional weight.

Step 3 − Add the product terms to obtain the equivalent decimal number.

Let us consider some examples to understand the binary to decimal conversion.

Example 1

Convert (101101)2 into decimal equivalent.

Solution

The given binary number is (101101)2

Step 1 − Defining positional weights for the given binary number −

| Bits | 1 | 0 | 1 | 1 | 0 | 1 |

| Weights | 25 | 24 | 23 | 22 | 21 | 20 |

Step 2 − Calculating product of bits and positional weights −

| Bits | Weights | Multiply | Product |

|---|---|---|---|

| 1 | 25 | 1 × 32 | 32 |

| 0 | 24 | 0 × 16 | 0 |

| 1 | 23 | 1 × 8 | 8 |

| 1 | 22 | 1 × 4 | 4 |

| 0 | 21 | 0 × 2 | 0 |

| 1 | 20 | 1 × 1 | 1 |

Step 3 − Add all the product terms to obtain the equivalent decimal number −

Decimal Number = 32 + 0 + 8 + 4 + 0 + 1 = (45)10

Hence, the decimal equivalent of (101101)2 is (45)10.

Example 2

Convert (1111011)2 into decimal equivalent.

Solution

Multiplying Bits with positional weights, we get,

Decimal Number = 1 × 26 + 1 × 25 + 1 × 24 + 1 × 23 + 0 × 22 + 1 × 21 + 1 × 20

Decimal Number = 64 + 32 + 16 + 8 + 0 + 2 + 1 = (123)10

Hence, the decimal equivalent of (1111011)2 is (123)10.

Example 3

Convert (1001.11)2 into decimal.

Solution

The given binary number has integer and fractional parts. The integer part is multiplied with positive weights, while the fractional part is multiplied with negative weights as follows −

Decimal Number = 1 × 23 + 0 × 22 + 0 × 21 + 1 × 20 + 1 × 2-1 + 1 × 2-2

Decimal Number = 8 + 0 + 0 + 1 + 0.5 + 0.25 = (9.75)10

Thus, the decimal equivalent of (1001.11)2 is (9.75)10.

Decimal to Binary Conversion

A decimal number can be converted to their equivalent binary number by using the double-dabble method. In this method, the integer part of the given decimal number is successively divided by 2 and the fractional part is successively multiplied by 2.

In the integer part, the remainders read from bottom to top give the integer part of the binary equivalent. In the fractional part, the carries read from top to bottom give the fractional part of the binary equivalent.

The following steps are followed to convert a decimal number to the binary equivalent −

Step 1 − Divide the integer part of the given decimal number successively by 2 and read the remainders from bottom to top.

Step 2 − Multiply the fractional part of the given decimal number successively by 2 and read the carries from top to bottom.

Let us see some examples to understand the conversion of a decimal number into its equivalent binary number.

Example 1

Convert (28)10 to binary equivalent.

Solution

The given decimal number is an integer. Thus, we divide the decimal number successively by 2 and read the remainders upwards to obtain the equivalent binary number.

| Decimal | Remainders | |

|---|---|---|

| 2 | 28 | |

| 2 | 14 | 0 |

| 2 | 7 | 0 |

| 2 | 3 | 1 |

| 2 | 1 | 1 |

| 0 | 1 |

Reading the remainders from bottom to top, the result will be (11100)2. It is the binary equivalent of (28)10.

Example 2

Convert (165.75)10 to its equivalent binary.

Solution

The given decimal number is a mixed number having both integer and fractional parts. Thus, to obtain its equivalent binary number, we convert the integer and fractional parts separately.

The binary equivalent of 16510 is obtained as follows,

| Decimal | Remainders | |

|---|---|---|

| 2 | 165 | |

| 2 | 82 | 1 |

| 2 | 41 | 0 |

| 2 | 20 | 1 |

| 2 | 10 | 0 |

| 2 | 5 | 0 |

| 2 | 2 | 1 |

| 2 | 1 | 0 |

| 0 | 1 |

Reading the remainders from bottom to top, the binary equivalent of 16510 is (10100101)2.

Now, let's convert the Fractional Part (0.75) of the given number.

To convert the given decimal fraction into binary, we multiply it by 2, as follows,

| Decimal | Product | Carry |

|---|---|---|

| 0.75 × 2 | 1.5 | 1 |

| 0.5 × 2 | 1.0 | 1 |

| 0 × 2 | 0 |

Reading the carries from top to bottom, the result is 0.11. Thus, the binary equivalent of (0.75)10 is (0.11)2.

Therefore, (165.75)10 = (10100101.11)2

Binary to Octal Conversion

A binary number can be converted into its equivalent octal number by mapping method. The conversion of a binary number to the octal equivalent is done as per the following steps −

Step 1 − Starting from the binary point, make groups of 3-bits on both sides of the binary point.

Step 2 − Replace each group of 3-bit binary by the equivalent octal digit.

The following table shows the equivalent octal digital for each 3-bit binary group −

| Octal | Binary | ||

|---|---|---|---|

| (2)2 = 4 | (2)1 = 2 | (2)0 = 1 | |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 |

| 4 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 |

| 7 | 1 | 1 | 1 |

Let us understand the binary to octal conversion with the help of examples.

Example 1

Convert (110011101.110101)2 to its octal equivalent.

Solution

The binary to octal conversion will be performed as follows −

| 3-bit Group | 110 | 011 | 101 | . | 110 | 101 |

| Octal Equivalent | 6 | 3 | 5 | . | 6 | 5 |

Hence, the octal equivalent of given binary number is (635.65)8.

Example 2

Convert (1110111011.11101)2 to octal equivalent.

Solution

The conversion of given binary number to octal number is given below −

| 3-bit Group | 1 | 110 | 111 | 011 | . | 111 | 01 |

| 011 | 110 | 111 | 011 | . | 111 | 010 | |

| Octal Equivalent | 3 | 6 | 7 | 3 | . | 7 | 2 |

Hence, the octal equivalent of (1110111011.11101)2 is (3673.72)8.

Octal to Binary Conversion

We can also use the mapping method to convert an octal number into its equivalent binary number. In this method, we just replace each digital of the given octal number by its 3-bit binary equivalent.

Let’s understand the conversion of octal number to binary equivalent with the help of examples.

Example 1

Convert (3572.126)8 to binary equivalent.

Solution

The given octal number is converted into binary equivalent as follows −

| Octal Number | 3 | 5 | 7 | 2 | . | 1 | 2 | 6 |

| 3-bit Binary Equivalent | 011 | 101 | 111 | 010 | . | 001 | 010 | 110 |

Hence, the binary equivalent of (3572.126)8 is (011101111010.001010110)2.

Example 2

Convert (364.52)8 to its binary equivalent.

Solution

The conversion of given octal number to its equivalent binary number is given below −

| Octal Number | 3 | 6 | 4 | . | 5 | 2 |

| 3-bit Binary Equivalent | 011 | 110 | 100 | . | 101 | 010 |

Thus, the binary equivalent of the octal number (364.52)8 is (011110100.101010)2.

Octal to Decimal Conversion

The conversion of an octal number to its equivalent decimal number is same as the binary to decimal conversion. To convert an octal number to its decimal equivalent, we multiply each digit of the octal number by its positional weight and then add all the product terms to obtain the equivalent decimal number.

The step-by-step procedure to convert an octal number to its equivalent decimal number is given below −

Step 1 − Write the positional weights for each octal digit.

Step 2 − Multiply each octal digit with its positional weight.

Step 3 − Add the product terms to obtain the equivalent decimal number.

Let us understand the conversion of octal number to decimal number with the help of examples.

Example 1

Convert (356.25)8 to its decimal equivalent.

Solution

The given octal number can be converted to equivalent decimal number as follows −

| Octal Digits | Positional Weights | Multiply | Product |

|---|---|---|---|

| 3 | (8)2 | 3 × (8)2 | 192 |

| 5 | (8)1 | 5 × (8)1 | 40 |

| 6 | (8)0 | 6 × (8)0 | 6 |

| . | . | . | . |

| 2 | (8)-1 | 2 × (8)-1 | 0.25 |

| 5 | (8)-2 | 5 × (8)-2 | 0.078 |

Adding all the product terms to obtain the equivalent decimal number,

(356.25)8 = 192 + 40 + 6 + 0.25 + 0.078 = (238.328)10

Example 2

Convert (527.322)8 to its decimal equivalent.

Solution

We can convert the given octal number to its equivalent decimal number as follows −

| Octal Digits | Positional Weights | Multiply | Product |

|---|---|---|---|

| 5 | (8)2 | 5 × (8)2 | 320 |

| 2 | (8)1 | 2 × (8)1 | 16 |

| 7 | (8)0 | 7 × (8)0 | 7 |

| . | . | . | . |

| 3 | (8)-1 | 3 × (8)-1 | 0.375 |

| 2 | (8)-2 | 2 × (8)-2 | 0.0313 |

| 2 | (8)-3 | 2 × (8)-3 | 0.004 |

Add all the product terms to obtain the result,

(527.322)8 = 320 + 16 + 7 + 0.375 + 0.0313 + 0.004 = (343.4103)10

Decimal to Octal Conversion

We can convert a mixed decimal number (having integer and fractional parts) to its equivalent octal number. For this, we convert the integer and fractional parts separately.

To convert the integer part of the given decimal number to octal, we divide the given decimal number successively by 8 till the quotient is 0. The octal equivalent is obtained by reading the remainders from bottom to top, where the last remainder will be the most significant digit.

To convert the fractional part of the given decimal number to octal, we multiply the given decimal fraction successively by 8 till the product is 0 or the desired accuracy is obtained. The fractional part of the equivalent octal number is obtained by reading the carries from top to bottom.

Let’s understand the decimal to octal conversion with the help of examples.

Example

Convert (589.278)10 to octal.

Solution

The given decimal number is a mixed number with 589 as integer part and 0.278 as fractional part. Thus, we first convert the integer part to octal and then we convert the fractional part to octal.

Converting Integer Part (589)10 to Octal −

| Decimal | Remainders | |

|---|---|---|

| 8 | 589 | |

| 8 | 73 | 5 |

| 8 | 9 | 1 |

| 8 | 1 | 1 |

| 0 | 1 |

Reading the remainders from bottom to top, the equivalent octal of (589)10 is (1115)8.

Converting the Fractional Part (0.278)10 to Octal −

| Decimal | Product | Carry |

|---|---|---|

| 0.278 × 8 | 2.224 | 2 |

| 0.224 × 8 | 1.792 | 1 |

| 0.792 × 8 | 6.336 | 6 |

| 0.336 × 8 | 2.688 | 2 |

Reading the carries from top to bottom to obtain the fractional part of the equivalent octal number, the result is (0.2162)8.

Thus, the equivalent octal number of (589.278)10 is (1115.2162)8.

Hexadecimal to Binary Conversion

We can convert a hexadecimal number into its equivalent binary by using the mapping method. In this method, we replace each digit of the given hexadecimal number by its equivalent 4-bit binary group.

The following table shows the equivalent 4-bit binary group of each hexadecimal digit −

| Hexadecimal | Binary | |||

|---|---|---|---|---|

| (2)3 = 8 | (2)2 = 4 | (2)1 = 2 | (2)0 = 1 | |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| A (10) | 1 | 0 | 1 | 0 |

| B (11) | 1 | 0 | 1 | 1 |

| C (12) | 1 | 1 | 0 | 0 |

| D (13) | 1 | 1 | 0 | 1 |

| E (14) | 1 | 1 | 1 | 0 |

| F (15) | 1 | 1 | 1 | 1 |

Let us understand the conversion of a hexadecimal number to binary number with the help of examples.

Example 1

Convert (3A94.C5D)16 to binary equivalent.

Solution

The given hexadecimal number can be converted into equivalent binary number as follows −

| Hexadecimal Number | 3 | A | 9 | 4 | . | C | 5 | D |

| 3 | 10 | 9 | 4 | . | 12 | 5 | 13 | |

| 4-bit Binary Equivalent | 0011 | 1010 | 1001 | 0100 | . | 1100 | 0101 | 1101 |

Thus, the binary equivalent of the given hexadecimal number is (0011101010010100.110001011101)2.

Example 2

Convert (ABD.2E)16 to binary equivalent.

Solution

The conversion of given hexadecimal number to its binary is done as follows −

| Hexadecimal Number | A | B | D | . | 2 | E |

| 10 | 11 | 13 | . | 2 | 14 | |

| 4-bit Binary Equivalent | 1010 | 1011 | 1101 | . | 0010 | 1110 |

Hence, the equivalent binary of (ABD.2E)16 is (101010111101.00101110)2.

Binary to Hexadecimal Conversion

To convert a given binary number to its equivalent hexadecimal number, we create groups of 4 bits each on both sides of the binary point. Then, we replace each group of 4-bit binary by the equivalent hexadecimal digit.

Let us understand the conversion of a binary number to its equivalent hexadecimal with the help of examples.

Example 1

Convert (1110111001101.111011)2 to hexadecimal.

Solution

The conversion of the given binary number to hexadecimal equivalent is done as follows −

| 4-bit Group | 1 | 1101 | 1100 | 1101 | . | 1110 | 11 |

| 0001 | 1101 | 1100 | 1101 | . | 1110 | 1100 | |

| Hexadecimal Equivalent | 1 | D | C | D | . | E | C |

Thus, the hexadecimal equivalent of the given binary number is (1DCD.EC)16.

Example 2

Convert (110111110111.1100)2 to hexadecimal.

Solution

We can convert the given binary number into hexadecimal equivalent as follows −

| 4-bit Group | 1101 | 1111 | 0111 | . | 1100 |

| Hexadecimal Equivalent | D | F | 7 | . | C |

Thus, the hexadecimal equivalent of (110111110111.1100)2 is (DF7.C)16.

Hexadecimal to Decimal Conversion

To convert a hexadecimal number to its equivalent decimal number, we multiply each digit in the hexadecimal number by its positional weight and then add all the product terms to obtain the final result.

The step-by-step procedure to convert a hexadecimal number to its equivalent decimal number is explained below −

Step 1 − Write the positional weights for each hexadecimal digit.

Step 2 − Multiply each hexadecimal digit with its positional weight.

Step 3 − Add the product terms to obtain the equivalent decimal number.

Let us see some examples to understand the conversion of hexadecimal to decimal number.

Example 1

Convert (5AB2.8C)16 to decimal equivalent.

Solution

The conversion of the given hexadecimal number to its decimal equivalent is given below −

| Hex Digits | Decimal Equiv. | Positional Weights | Multiply | Product |

|---|---|---|---|---|

| 5 | 5 | (16)3 | 5 × (16)3 | 20480 |

| A | 10 | (16)2 | 10 × (16)2 | 2560 |

| B | 11 | (16)1 | 11 × (16)1 | 176 |

| 2 | 2 | (16)0 | 2 × (16)0 | 2 |

| . | . | . | . | . |

| 8 | 8 | (16)-1 | 8 × (16)-1 | 0.5 |

| C | 12 | (16)-2 | 12 × (16)-2 | 0.0468 |

Add all the product terms to obtain the equivalent decimal,

(5AB2.8C)16 = 20480 + 2560 + 176 + 2 + 0.5 + 0.0468 = (23218.5468)10

Example 2

Convert (1AF.2)16 to decimal.

Solution

The decimal equivalent of the given hexadecimal number can be obtained as follows −

| Hex Digits | Decimal Equiv. | Positional Weights | Multiply | Product |

|---|---|---|---|---|

| 1 | 1 | (16)2 | 1 × (16)2 | 256 |

| A | 10 | (16)1 | 10 × (16)1 | 160 |

| F | 15 | (16)0 | 15 × (16)0 | 15 |

| . | . | . | . | . |

| 2 | 2 | (16)-1 | 2 × (16)-1 | 0.125 |

Adding the product terms to obtain the equivalent decimal number,

(1AF.2)16 = 256 + 160 + 15 + 0.125 = (431.125)10

Decimal to Hexadecimal Conversion

If a mixed decimal number is given that has integer and fraction parts. Then, to convert the given decimal number to its equivalent hexadecimal, we convert integer and fraction parts separately.

To convert the integer part, we successively divide the decimal integer by 16 till the quotient is 0. The integer part of the equivalent hexadecimal is obtained by reading the remainders from bottom to top.

To convert the fractional part, we multiply the decimal fractional number by 16 till the product is 0 or till the desired accuracy is obtained. The fractional part of the equivalent hexadecimal is obtained by reading the carries from top to bottom.

Let us see some examples to understand the decimal to hexadecimal conversion.

Example

Convert (524.26)10 to hexadecimal.

Solution

The given decimal number is a mixed number. Hence, we have to convert its integer and fractional parts separately.

Converting Integer Part (524)10 to Hexadecimal −

| Decimal | Remainders | |

|---|---|---|

| 16 | 524 | |

| 16 | 32 | 12 (C) |

| 16 | 2 | 0 |

| 0 | 2 |

Reading the remainder from bottom to top to obtained the hexadecimal equivalent, the result is (20C)16.

Converting Fractional Part (0.26)10 to Hexadecimal −

| Decimal | Product | Carry |

|---|---|---|

| 0.26 × 16 | 4.16 | 4 |

| 0.16 × 16 | 2.56 | 2 |

| 0.56 × 16 | 8.96 | 8 |

| 0.96 × 16 | 15.36 | 15 (F) |

Reading the carries from top to bottom to obtain the equivalent hexadecimal number, the result is (0.428F)16.

Thus, the hexadecimal equivalent of the decimal number (524.26)10 is (20C.428F)16.

Octal to Hexadecimal Conversion

The conversion of octal to hexadecimal is very simple. We first convert the given octal number to binary and then the binary number to the hexadecimal.

The step-by-step process to convert a given octal number to its equivalent hexadecimal is given below −

Step 1 − Convert each digit of the given octal number to its equivalent binary of 3-bits.

Step 2 − Make groups of 4 bits each of the obtained binary number.

Step 3 − Convert each 4-bit binary group to its equivalent hexadecimal.

Let us see some examples to understand the conversion of octal to hexadecimal.

Example 1

Convert (742.35)8 to hexadecimal.

Solution

The conversion of given octal number to hexadecimal is explained below −

| Octal Digits | 3-bit Binary | 4-bit Binary | Hex Digits |

|---|---|---|---|

| 7 | 111 | 0001 | 1 |

| 4 | 100 | 1110 | E |

| 2 | 010 | 0010 | 2 |

| . | . | . | . |

| 3 | 011 | 0111 | 7 |

| 5 | 101 | 0100 | 4 |

Thus, the hexadecimal equivalent of the given octal number is (1E2.74)16.

Example 2

Convert (1523.742)8 to hexadecimal.

Solution

The following table demonstrates the conversion of given octal number to hexadecimal −

| Octal Digits | 3-bit Binary | 4-bit Binary | Hex Digits |

|---|---|---|---|

| 1 | 001 | 0000 | 0 |

| 5 | 101 | 0011 | 3 |

| 2 | 010 | 0101 | 5 |

| 3 | 011 | 0011 | 3 |

| . | . | . | . |

| 7 | 111 | 1111 | F |

| 4 | 100 | 0001 | 1 |

| 2 | 010 | 0000 | 0 |

Hence, the hexadecimal equivalent of the given octal number is (353.F1)16.

Hexadecimal to Octal Conversion

The hexadecimal to octal conversion can be perform in the same way as the octal to hexadecimal as explained above. To convert a given hexadecimal number to octal number, we first convert the given hexadecimal number to binary and then the binary number to the octal.

The step-by-step procedure to convert a hexadecimal number to its equivalent octal number is explained below −

Step 1 − Convert each hexadecimal digit to its equivalent 4-bit binary.

Step 2 − Make groups of 3-bits each of the obtained binary number.

Step 3 − Convert each 3-bit binary group to its equivalent octal number.

The following examples demonstrate the method of converting a given hexadecimal number to its equivalent octal number.

Example 1

Convert (B3A9.5F)16 to octal.

Solution

The conversion of the given hexadecimal number to its equivalent octal number is explained below −

| Hex Digits | B | 3 | A | 9 | . | 5 | F | |||

| 4-bit Binary | 1011 | 0011 | 1010 | 1001 | . | 0101 | 1111 | |||

| 3-bit Binary | 001 | 011 | 001 | 110 | 101 | 001 | . | 010 | 111 | 110 |

| Octal Digits | 1 | 3 | 1 | 6 | 5 | 1 | . | 2 | 7 | 6 |

Thus, the octal equivalent of the given hexadecimal number is (131651.276)8.

Example 2

Convert (AC.F)16 to octal.

Solution

The conversion of given hexadecimal number to its equivalent octal number is demonstrated below −

| Hex Digits | A | C | . | F | ||

| 10 | 12 | . | 15 | |||

| 4-bit Binary | 1010 | 1100 | . | 1111 | ||

| 3-bit Binary | 010 | 101 | 100 | . | 111 | 100 |

| Octal Digits | 2 | 5 | 4 | . | 7 | 4 |

Hence, the octal equivalent of the given hexadecimal number is (254.74)8.

Conclusion

We can convert a given number from one base to another. Number system conversion is one the important operations in the field of digital electronics, as it allows to represent the same information in different formats. In this chapter, we explained all the possible number system conversions with the help of examples.

Binary Numbers Representation

We can categorize binary numbers into two groups Unsigned numbers and Signed numbers. Read this chapter to learn how signed and unsigned binary numbers are represented. We will also explain how you can find out the 1's and 2's complement form of signed binary numbers.

Unsigned Numbers

Unsigned numbers contain only magnitude of the number. They don’t have any sign. That means all unsigned binary numbers are positive. As in decimal number system, the placing of positive sign in front of the number is optional for representing positive numbers. Therefore, all positive numbers including zero can be treated as unsigned numbers if positive sign is not assigned in front of the number.

Signed Numbers

Signed numbers contain both sign and magnitude of the number. Generally, the sign is placed in front of number. So, we have to consider the positive sign for positive numbers and negative sign for negative numbers. Therefore, all numbers can be treated as signed numbers if the corresponding sign is assigned in front of the number.

If sign bit is zero, which indicates the binary number is positive. Similarly, if sign bit is one, which indicates the binary number is negative.

Representation of Un-Signed Binary Numbers

The bits present in the un-signed binary number holds the magnitude of a number. That means, if the un-signed binary number contains ‘N’ bits, then all N bits represent the magnitude of the number, since it doesn’t have any sign bit.

Example

Consider the decimal number 108. The binary equivalent of this number is 1101100. This is the representation of unsigned binary number.

(108)10 = (1101100)2

It is having 7 bits. These 7 bits represent the magnitude of the number 108.

Representation of Signed Binary Numbers

The Most Significant Bit (MSB) of signed binary numbers is used to indicate the sign of the numbers. Hence, it is also called as sign bit. The positive sign is represented by placing ‘0’ in the sign bit. Similarly, the negative sign is represented by placing ‘1’ in the sign bit.

If the signed binary number contains ‘N’ bits, then (N-1) bits only represent the magnitude of the number since one bit (MSB) is reserved for representing sign of the number.

There are three types of representations for signed binary numbers

- Sign-Magnitude form

- 1’s complement form

- 2’s complement form

Representation of a positive number in all these 3 forms is same. But, only the representation of negative number will differ in each form.

Consider the positive decimal number +108. The binary equivalent of magnitude of this number is 1101100. These 7 bits represent the magnitude of the number 108. Since it is positive number, consider the sign bit as zero, which is placed on left most side of magnitude.

(+108)10 = (01101100)2

Therefore, the signed binary representation of positive decimal number +108 is 𝟎𝟏𝟏𝟎𝟏𝟏𝟎𝟎. So, the same representation is valid in sign-magnitude form, 1’s complement form and 2’s complement form for positive decimal number +108.

Sign-Magnitude form

In sign-magnitude form, the MSB is used for representing sign of the number and the remaining bits represent the magnitude of the number. So, just include sign bit at the left most side of unsigned binary number. This representation is similar to the signed decimal numbers representation.

Example

Consider the negative decimal number -108. The magnitude of this number is 108. We know the unsigned binary representation of 108 is 1101100. It is having 7 bits. All these bits represent the magnitude.

Since the given number is negative, consider the sign bit as one, which is placed on left most side of magnitude.

(−108)10 = (11101100)2

Therefore, the sign-magnitude representation of -108 is 11101100.

1’s complement form

The 1’s complement of a number is obtained by complementing all the bits of signed binary number. So, 1’s complement of positive number gives a negative number. Similarly, 1’s complement of negative number gives a positive number.

That means, if you perform two times 1’s complement of a binary number including sign bit, then you will get the original signed binary number.

Example

Consider the negative decimal number -108. The magnitude of this number is 108. We know the signed binary representation of 108 is 01101100.

It is having 8 bits. The MSB of this number is zero, which indicates positive number. Complement of zero is one and vice-versa. So, replace zeros by ones and ones by zeros in order to get the negative number.

(−108)10 = (10010011)2

Therefore, the 1’s complement of (108)10 is (10010011)2.

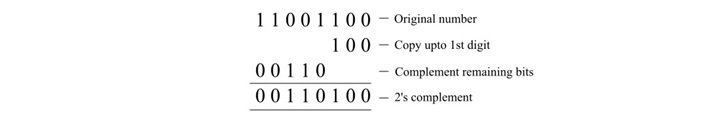

2’s complement form