- 数字电子教程

- 数字电子 - 首页

- 数字电子基础

- 数字系统类型

- 信号类型

- 逻辑电平和脉冲波形

- 数字系统组件

- 数字逻辑运算

- 数字系统优势

- 数制

- 数制

- 二进制数表示

- 二进制运算

- 有符号二进制运算

- 八进制运算

- 十六进制运算

- 补码运算

- 进制转换

- 进制转换

- 二进制到十进制转换

- 十进制到二进制转换

- 二进制到八进制转换

- 八进制到二进制转换

- 八进制到十进制转换

- 十进制到八进制转换

- 十六进制到二进制转换

- 二进制到十六进制转换

- 十六进制到十进制转换

- 十进制到十六进制转换

- 八进制到十六进制转换

- 十六进制到八进制转换

- 二进制编码

- 二进制编码

- 8421 BCD码

- 余3码

- 格雷码

- ASCII码

- EBCDIC码

- 代码转换

- 错误检测与纠错码

- 逻辑门

- 逻辑门

- 与门

- 或门

- 非门

- 通用门

- 异或门

- 异或非门

- CMOS逻辑门

- 使用二极管电阻逻辑的或门

- 与门与或门

- 两级逻辑实现

- 阈值逻辑

- 布尔代数

- 布尔代数

- 布尔代数定律

- 布尔函数

- 德摩根定理

- SOP和POS形式

- POS到标准POS形式

- 最小化技术

- 卡诺图最小化

- 三变量卡诺图

- 四变量卡诺图

- 五变量卡诺图

- 六变量卡诺图

- 无关项

- 奎因-麦克斯拉斯基法

- 最小项和最大项

- 规范式和标准式

- 最大项表示

- 使用布尔代数简化

- 组合逻辑电路

- 数字组合电路

- 数字算术电路

- 多路复用器

- 多路复用器设计流程

- MUX通用门

- 使用4:1 MUX的2变量函数

- 使用8:1 MUX的3变量函数

- 多路分解器

- MUX与DEMUX

- 奇偶校验位生成器和校验器

- 比较器

- 编码器

- 键盘编码器

- 优先编码器

- 译码器

- 算术逻辑单元

- 7段LED显示器

- 代码转换器

- 代码转换器

- 二进制到十进制转换器

- 十进制到BCD转换器

- BCD到十进制转换器

- 二进制到格雷码转换器

- 格雷码到二进制转换器

- BCD到余3码转换器

- 余3码到BCD转换器

- 加法器

- 半加器

- 全加器

- 串行加法器

- 并行加法器

- 使用半加器的全加器

- 半加器与全加器

- 使用与非门的全加器

- 使用与非门的半加器

- 二进制加法/减法器

- 减法器

- 半减器

- 全减器

- 并行减法器

- 使用2个半减器的全减器

- 使用与非门的半减器

- 时序逻辑电路

- 数字时序电路

- 时钟信号和触发

- 锁存器

- 移位寄存器

- 移位寄存器应用

- 二进制寄存器

- 双向移位寄存器

- 计数器

- 二进制计数器

- 非二进制计数器

- 同步计数器设计

- 同步计数器与异步计数器

- 有限状态机

- 算法状态机

- 触发器

- 触发器

- 触发器转换

- D触发器

- JK触发器

- T触发器

- SR触发器

- 带时钟的SR触发器

- 无时钟的SR触发器

- 带时钟的JK触发器

- JK到T触发器

- SR到JK触发器

- 触发方式:触发器

- 边沿触发触发器

- 主从JK触发器

- 竞争冒险现象

- A/D和D/A转换器

- 模数转换器

- 数模转换器

- DAC和ADC集成电路

- 逻辑门的实现

- 用与非门实现非门

- 用与非门实现或门

- 用与非门实现与门

- 用与非门实现或非门

- 用与非门实现异或门

- 用与非门实现异或非门

- 用或非门实现非门

- 用或非门实现或门

- 用或非门实现与门

- 用或非门实现与非门

- 用或非门实现异或门

- 用或非门实现异或非门

- 使用CMOS的与非/或非门

- 使用与非门的全减器

- 使用2:1 MUX的与门

- 使用2:1 MUX的或门

- 使用2:1 MUX的非门

- 存储器件

- 存储器件

- RAM和ROM

- 高速缓存存储器设计

- 可编程逻辑器件

- 可编程逻辑器件

- 可编程逻辑阵列

- 可编程阵列逻辑

- 现场可编程门阵列

- 数字电子系列

- 数字电子系列

- CPU架构

- CPU架构

- 数字电子资源

- 数字电子 - 快速指南

- 数字电子 - 资源

- 数字电子 - 讨论

可编程逻辑器件

可编程逻辑器件 (PLD) 是一组集成电路,可以配置为执行各种逻辑功能。PLD 在工程和技术领域发挥着重要作用,因为它们构成了创新的基础,并支持工程师开发自动化数字系统以提高流程的灵活性和效率。这里,“可编程”意味着定义一个可以多次执行而无需人工干预的功能。

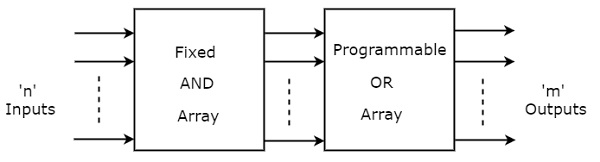

可编程逻辑器件(PLD) 是集成电路。它们包含一个与门阵列和另一个或门阵列。根据具有可编程功能的阵列类型,有三种类型的 PLD。

- 可编程只读存储器

- 可编程阵列逻辑

- 可编程逻辑阵列

将信息输入这些设备的过程称为编程。基本上,用户可以对这些器件或集成电路进行电气编程,以根据需要实现布尔函数。这里,术语“编程”指的是硬件编程,而不是软件编程。

在本章中,我们将解释可编程逻辑器件的基本概念、类型、优点、局限性和应用。

可编程只读存储器 (PROM)

只读存储器 (ROM) 是一种存储器设备,它永久地存储二进制信息。这意味着,我们以后无法通过任何方式更改存储的信息。如果ROM具有可编程功能,则称为可编程ROM (PROM)。用户可以使用PROM编程器一次电气编程二进制信息。

PROM是一种可编程逻辑器件,具有固定与阵列和可编程或阵列。PROM的框图如下所示。

这里,与门的输入不是可编程类型。因此,我们必须使用2n个具有n个输入的与门来生成2n个积项。我们可以使用nx2n译码器实现这些积项。因此,此译码器生成“n”个最小项。

这里,或门的输入是可编程的。这意味着,我们可以编程任何数量所需的积项,因为所有与门的输出都作为输入应用于每个或门。因此,PROM的输出将以最小项之和的形式出现。

示例

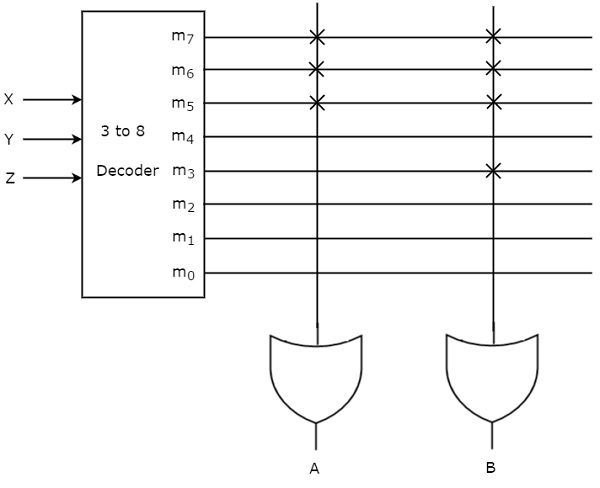

让我们使用PROM实现以下布尔函数。

$$\mathrm{A(X,Y,Z)\:=\:\sum m\left ( 5,6,7 \right )}$$

$$\mathrm{B(X,Y,Z)\:=\:\sum m\left ( 3,5,6,7 \right )}$$

给定的两个函数以最小项之和的形式给出,每个函数都有三个变量X、Y和Z。因此,我们需要一个3到8译码器和两个可编程或门来产生这两个函数。相应的PROM如下所示。

这里,3到8译码器生成八个最小项。两个可编程或门可以访问所有这些最小项。但是,为了通过每个或门产生相应的布尔函数,仅对所需的最小项进行编程。符号“X”用于可编程连接。

什么是可编程逻辑器件?

可编程逻辑器件 (PLD) 可以定义为可以编程以执行特定功能的集成电路 (IC)。这里,编程意味着我们可以定义一组可以执行以多次执行功能的指令,而无需任何人工干预。

开发PLD的主要需求是实现可以复制传统逻辑电路行为并多次复制它的数字逻辑功能。但是,PLD在可编程性方面不同于普通的数字逻辑电路,这意味着我们可以通过在器件中设置一组指令来定义所需的逻辑功能。

PLD类型

根据所用器件的类型,可编程逻辑器件 (PLD) 可以分为以下两种类型:

- 双极型PLD

- CMOS PLD

让我们详细讨论每种类型的可编程逻辑器件。

双极型PLD

双极型PLD是可编程逻辑器件的类型,其中双极结型晶体管 (BJT) 是主要的功能器件。双极型PLD是可编程逻辑器件的早期版本。因此,在开发CMOS PLD之前,它们被广泛使用。

以下是双极型可编程逻辑器件的一些重要特性:

- 双极型PLD提供快速的开关速度,因此它们可以在更高的频率下工作。

- 双极型PLD更适合涉及快速信号处理并需要快速响应时间的应用。

- 双极型PLD需要更多的功率来运行。

- 双极型PLD对电子噪声和干扰具有更好的免疫力。

所有这些特性使双极型可编程逻辑器件非常适合用于高速运行和可靠性至关重要的应用,例如航空航天、军事和电信系统。

CMOS PLD

CMOS PLD代表互补金属氧化物半导体可编程逻辑器件。顾名思义,CMOS PLD使用CMOS晶体管,即NMOS(N沟道金属氧化物半导体)和PMOS(P沟道金属氧化物半导体)晶体管作为基本组件。

CMOS PLD基本上是PLD的现代版本,由于其众多优点,在现代数字系统中得到广泛使用。

下面描述了CMOS PLD的一些重要特性:

- CMOS PLD运行所需的功率非常少。因此,此特性使CMOS PLD非常适合用于电池供电设备,在这些设备中,能源效率是一个重要因素。

- CMOS PLD更可靠且更健壮。因为它们设计用于承受各种环境因素,例如高温/低温、电压波动和不同的辐射干扰。

- CMOS PLD在可扩展性方面也很出色。

CMOS PLD是更新的PLD器件,因此在各种现代电子设备中非常常用,例如消费电子产品、医疗设备、工业自动化系统、汽车系统。

PLD编程语言

在可编程逻辑器件(PLD)的情况下,使用多种不同的硬件描述语言(HDL)对其进行编程。使用这些PLD编程语言,工程师和设计师可以定义PLD电路的行为和逻辑功能。

这里描述了一些最常用的PLD编程语言:

VHDL

VHDL代表VHSIC硬件描述语言。它是一种标准化的硬件描述语言,用于对数字电路和系统进行建模和仿真。使用VHDL,工程师和开发人员可以指定数字电路的结构和功能。VHDL非常适合组合电路和时序电路,因为它支持并发和顺序描述。

VHDL是设计和验证高度复杂的数字电路和系统(如PLD、ASIC、FPGA等)最广泛使用的编程语言之一。

Verilog

Verilog也是一种硬件描述语言(HDL),用于设计和编程PLD。与VHDL类似,Verilog也支持并发和顺序描述,使工程师和设计师能够定义数字电路的结构和行为。

这种编程语言最常用于半导体行业,用于设计和编程各种数字系统。

PALASM

PALASM代表可编程阵列逻辑汇编器。它也是一种用于编程可编程逻辑器件(PLD)的硬件描述语言(HDL)和汇编器。在PALASM的情况下,PLD的行为、逻辑功能和结构使用文本语言格式进行描述。因此,开发人员必须编写PALASM代码来描述所需的逻辑功能和互连。之后,这些代码被组装成适合可编程逻辑器件的格式。

然而,PALASM是一种较旧的硬件描述语言,在20世纪80年代和90年代初被广泛用于开发基于PLD的逻辑电路。

ABEL

ABEL代表高级布尔表达式语言。它是一种为编程可编程逻辑器件(PLD)而开发的高级硬件描述语言。

在ABEL中,逻辑方程式、真值表和寄存器传输级设计描述使用易于阅读的语法进行指定。然后,ABEL编译器将所有这些设计描述转换为适合编程所需PLD的格式。ABEL在20世纪90年代是一种非常常用的用户友好型硬件描述语言。

CUPL

CUPL代表通用可编程逻辑编译器。它也是一种用于编程各种PLD的硬件描述语言(HDL)和编译器。在这种编程语言中,逻辑函数、真值表和时序逻辑指令以简单的语法形式指定。

这种HDL语言在20世纪90年代和21世纪初也很流行,用于设计基于PLD的逻辑电路。

所有这些都是一些用于设计和编程可编程逻辑器件的重要编程语言。PALASM、ABEL和CUPL语言主要用于低复杂度的器件。而VHDL和Verilog则用于编程现代的高复杂度PLD。

可编程逻辑器件的优点

可编程逻辑器件(PLD)具有许多优点,使其成为数字系统设计领域的重要工具。以下是可编程逻辑器件的一些重要优势:

- 可编程逻辑器件(PLD)易于编程和重新编程。因此,它们在设计和实现各种逻辑功能方面提供了显著的灵活性。

- PLD允许设计定制的逻辑电路以满足应用的特定需求。这可以通过编程器件的内部逻辑电路来实现。

- PLD可用于数字电路的原型设计和测试,这有助于更快地进行新产品开发。通过加速产品开发过程,PLD有助于减少硬件设计中涉及的时间和成本。

- PLD提供了一种快速且经济高效的方式来开发中到复杂的数字逻辑电路和系统。PLD通过将大量逻辑功能和组件集成到单个器件中,有助于开发简单、廉价且紧凑的数字系统。

- PLD还支持现代处理技术,如并行处理、流水线处理等。此功能有助于通过同时执行逻辑功能来实现高性能。

可编程逻辑器件的局限性

可编程逻辑器件(PLD)提供了上面讨论的几个优点,但它们也有一些局限性。以下是可编程逻辑器件的一些主要局限性:

- 可编程逻辑器件可以设计为支持有限数量的逻辑功能和元素。因此,复杂数字电路的实现可能需要多个器件。

- PLD通常具有固定数量的输入/输出(I/O)引脚。此限制可能会导致连接性和与外部/外围设备接口方面的问题。

- PLD的编程需要硬件描述语言(HDL)和设计工具的知识。有时,由于意外重新编程或数据损坏,PLD可能会出现故障。

- PLD本身并不支持通用处理器中使用的复杂算术运算和其他高级编程运算。因此,开发人员必须通过定制逻辑设计来实现此类运算和功能。

可编程逻辑器件的应用

可编程逻辑器件(PLD)广泛应用于各个领域和行业,用于设计数字逻辑电路和实现各种逻辑功能。以下是可编程逻辑器件的一些常见应用:

- PLD广泛用于嵌入式系统,执行不同的实时操作,如控制、接口和数据处理。

- 在数字信号处理领域,PLD用于设计数字滤波器、开发调制解调器算法、执行信号处理等。

- PLD在通信系统中发挥着重要作用,因为它们有助于执行各种操作,如信号路由、数据加密和解密、协议转换等。

- 在航空航天和国防领域,PLD用于完成各种关键功能,如飞行控制、操作雷达系统、引导导弹、加密机密数据等。

- PLD也用于机器人和工业自动化,以控制和监控机械的操作。

- 在医疗设备中,PLD用于自动高速数据处理、医疗数据的实时分析、患者监测等。

结论

总之,可编程逻辑器件是一种可以编程或训练以执行特定逻辑功能的数字器件。它主要用于各种应用中的自动化和效率改进目的。

在本章中,我们解释了PLD的基本知识、类型、优点、局限性和应用。在下一章中,我们将探讨各种可编程逻辑器件及其功能和特性。