- 数字电子教程

- 数字电子 - 首页

- 数字电子基础

- 数字系统类型

- 信号类型

- 逻辑电平和脉冲波形

- 数字系统组件

- 数字逻辑运算

- 数字系统优势

- 数制

- 数制

- 二进制数表示

- 二进制运算

- 有符号二进制运算

- 八进制运算

- 十六进制运算

- 补码运算

- 进制转换

- 进制转换

- 二进制到十进制转换

- 十进制到二进制转换

- 二进制到八进制转换

- 八进制到二进制转换

- 八进制到十进制转换

- 十进制到八进制转换

- 十六进制到二进制转换

- 二进制到十六进制转换

- 十六进制到十进制转换

- 十进制到十六进制转换

- 八进制到十六进制转换

- 十六进制到八进制转换

- 二进制编码

- 二进制编码

- 8421 BCD 码

- 余3码

- 格雷码

- ASCII 码

- EBCDIC 码

- 代码转换

- 错误检测和纠错码

- 逻辑门

- 逻辑门

- 与门

- 或门

- 非门

- 通用门

- 异或门

- 异或非门

- CMOS 逻辑门

- 使用二极管电阻逻辑的或门

- 与门与或门

- 两级逻辑实现

- 阈值逻辑

- 布尔代数

- 布尔代数

- 布尔代数定律

- 布尔函数

- 德摩根定理

- SOP 和 POS 形式

- POS 到标准 POS 形式

- 最小化技术

- 卡诺图最小化

- 三变量卡诺图

- 四变量卡诺图

- 五变量卡诺图

- 六变量卡诺图

- 无关项条件

- 奎因-麦克斯拉斯基方法

- 最小项和最大项

- 规范式和标准式

- 最大项表示

- 使用布尔代数进行简化

- 组合逻辑电路

- 数字组合电路

- 数字算术电路

- 多路复用器

- 多路复用器设计流程

- 多路复用器通用门

- 使用 4:1 多路复用器的 2 变量函数

- 使用 8:1 多路复用器的 3 变量函数

- 多路分解器

- 多路复用器与多路分解器

- 奇偶校验位生成器和校验器

- 比较器

- 编码器

- 键盘编码器

- 优先编码器

- 译码器

- 算术逻辑单元

- 7 段 LED 显示器

- 代码转换器

- 代码转换器

- 二进制到十进制转换器

- 十进制到 BCD 转换器

- BCD 到十进制转换器

- 二进制到格雷码转换器

- 格雷码到二进制转换器

- BCD 到余 3 码转换器

- 余 3 码到 BCD 转换器

- 加法器

- 半加器

- 全加器

- 串行加法器

- 并行加法器

- 使用半加器的全加器

- 半加器与全加器

- 使用 NAND 门的全加器

- 使用 NAND 门的半加器

- 二进制加法/减法器

- 减法器

- 半减器

- 全减器

- 并行减法器

- 使用 2 个半减器的全减器

- 使用 NAND 门的半减器

- 时序逻辑电路

- 数字时序电路

- 时钟信号和触发

- 锁存器

- 移位寄存器

- 移位寄存器应用

- 二进制寄存器

- 双向移位寄存器

- 计数器

- 二进制计数器

- 非二进制计数器

- 同步计数器设计

- 同步计数器与异步计数器

- 有限状态机

- 算法状态机

- 触发器

- 触发器

- 触发器转换

- D 触发器

- JK 触发器

- T 触发器

- SR 触发器

- 带时钟的 SR 触发器

- 无时钟 SR 触发器

- 带时钟的 JK 触发器

- JK 到 T 触发器

- SR 到 JK 触发器

- 触发方法:触发器

- 边沿触发触发器

- 主从 JK 触发器

- 竞争冒险现象

- A/D 和 D/A 转换器

- 模数转换器

- 数模转换器

- DAC 和 ADC 集成电路

- 逻辑门的实现

- 使用 NAND 门的非门

- 使用 NAND 门的或门

- 使用 NAND 门的与门

- 使用 NAND 门的与非门

- 使用 NAND 门的异或门

- 使用 NAND 门的异或非门

- 使用 NOR 门的非门

- 使用 NOR 门的或门

- 使用 NOR 门的与门

- 使用 NOR 门的与非门

- 使用 NOR 门的异或门

- 使用 NOR 门的异或非门

- 使用 CMOS 的与非/与或非门

- 使用 NAND 门的全减器

- 使用 2:1 多路复用器的与门

- 使用 2:1 多路复用器的或门

- 使用 2:1 多路复用器的非门

- 存储器设备

- 存储器设备

- RAM 和 ROM

- 高速缓存存储器设计

- 可编程逻辑器件

- 可编程逻辑器件

- 可编程逻辑阵列

- 可编程阵列逻辑

- 现场可编程门阵列

- 数字电子系列

- 数字电子系列

- CPU 架构

- CPU 架构

- 数字电子资源

- 数字电子 - 快速指南

- 数字电子 - 资源

- 数字电子 - 讨论

异步或无时钟 SR 触发器

什么是 SR 触发器?

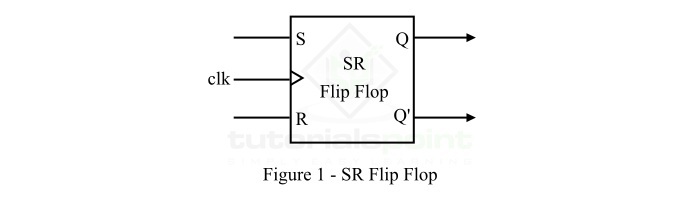

在数字电子学中,SR 触发器是一种时序逻辑电路,具有两个输入,即 S 和 R,以及两个输出,即 Q 和 Q'。

输入 S 代表“置位”,输入 R 代表“复位”。输出 Q 是触发器的正常输出,Q' 是触发器的反相输出,它是触发器正常输出 Q 的补码。SR 触发器是一种一位存储器件,用于多种数字电子系统。

SR 触发器的基本框图如图 1 所示。

根据时钟信号的有无,SR 触发器可分为两种类型,即同步 SR 触发器和异步 SR 触发器。同步 SR 触发器是在时钟信号激活时才产生输出的触发器。因此,它也称为带时钟的 SR 触发器。

另一方面,异步 SR 触发器是在任何时候将输入应用于电路时都可获得输出的触发器。异步 SR 触发器也称为无时钟 SR 触发器,因为其输出不受时钟信号控制,而仅受应用的输入控制。

正如本文标题所示,这里我们将只讨论异步或无时钟 SR 触发器。

什么是异步 SR 触发器?

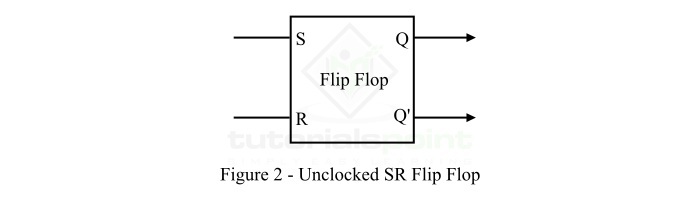

异步 SR 触发器,也称为无时钟 SR 触发器或简称 SR 锁存器,是一种用于存储一位二进制信息的时序逻辑电路。它有两个输入和两个输出。输入是触发器的 S(代表“置位”输入)和 R(代表“复位”输入)。第一个输出是 Q,称为触发器的正常输出,另一个输出是 Q',称为反相输出。

异步或无时钟 SR 触发器的框图如图 2 所示。

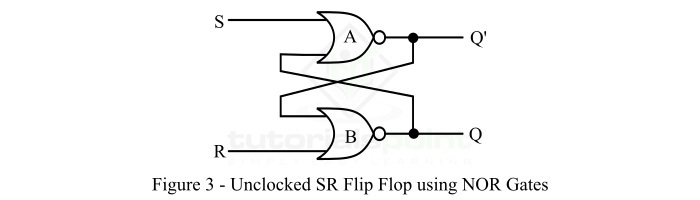

无时钟或异步 SR 触发器可以使用两个交叉耦合的 NOR 门或 NAND 门构建。

现在让我们讨论 SR 触发器的每种构建方式(使用 NOR 门和使用 NAND 门),以及它们的运行和真值表。

使用 NOR 门的异步 SR 触发器

如前所述,无时钟 SR 触发器可以使用两个交叉耦合的 NOR 门构建,如图 3 所示。

它有两个输入,即S(置位)和R(复位),以及两个输出,即Q(正常输出)和Q'(反相输出)。

对于 S 和 R 的不同可能输入组合,该异步 SR 触发器的操作如下所述:

- 当 S = 0 且 R = 0 时 - 在这种情况下,两个 NOR 门的输入都为逻辑 0。因此,对电路的输出没有影响。结果,输出保持其先前状态。无时钟 SR 触发器的这种状态称为“无变化”或“保持状态”。

- 当 S = 1 且 R = 0 时 - 在这种情况下,NOR 门 A 的输出将变为零,因为输入 S 为逻辑 1。结果,NOR 门 B 的两个输入都变为逻辑 0,因此 NOR 门 B 的输出为逻辑 1,使 Q 等于 1。这称为无时钟 SR 触发器的“置位状态”。

- 当 S = 0 且 R = 1 时 - 在这种情况下,NOR 门 B 的输出将变为零,因为输入 R 为逻辑 1,即 Q = 0。结果,NOR 门 A 的两个输入都变为逻辑 0,因此 NOR 门 A 的输出为逻辑 1,使 Q' 等于 1 且 Q = 0。这称为无时钟 SR 触发器的“复位状态”。

- 当 S = 1 且 R = 1 时 - 这称为 SR 触发器的“禁止状态”或“无效状态”,因为这种输入组合迫使两个 NOR 门的输出都变为逻辑 0,这是不可能的。

SR 触发器的真值表

基于上述描述的操作,无时钟 SR 触发器的真值表如下所示。

| S | R | Q | 描述 |

|---|---|---|---|

| 0 | 0 | NC | 无变化 |

| 0 | 1 | 0 | 复位 |

| 1 | 0 | 1 | 置位 |

| 1 | 1 | X | 禁止 |

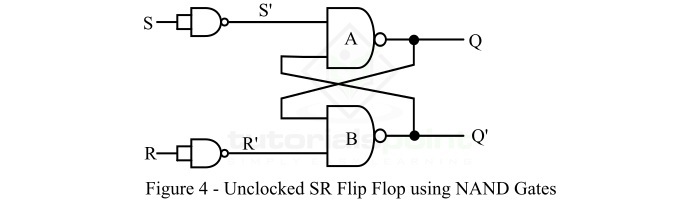

使用 NAND 门的异步 SR 触发器

我们还可以使用两个交叉耦合的 NAND 门实现无时钟 SR 触发器。使用 NAND 门的异步 SR 触发器如下面的图 4 所示。

可以看出,异步 SR 触发器是低电平有效的 SR 触发器。现在,让我们讨论异步 SR 触发器在不同可能的输入组合下的工作原理。

- 当 S = 0 且 R = 0 时,即 S' = 1 且 R' = 1 时 - 在这种情况下,两个输入即 S' 和 R' 都为逻辑 1,因此输出保持先前状态。这称为 SR 触发器的保持状态。

- 当 S = 0 且 R = 1 时,即 S' = 1 且 R' = 0 时 - 在这种情况下,输入 S' 为逻辑 1,输入 R' 为逻辑 0。因此,NAND 门 B 的输出将变为逻辑 1。因此,NAND 门 A 的输出,即 Q 变为逻辑 1。这称为触发器的复位状态。

- 当 S = 1 且 R = 0 时,即 S' = 0 且 R' = 1 时 - 在这种情况下,输入 S' 为逻辑 0,输入 R' 为逻辑 1。由于输入 S' 为逻辑 0,因此 NAND 门 A 的输出,即 Q 变为逻辑 1。这称为 SR 触发器的置位状态。

- 当 S = 1 且 R = 1 时,即 S' = 0 且 R' = 0 时 - 在这种情况下,两个输入都为逻辑 0,即两个 NAND 门的输出必须为逻辑 1,这是不允许的,因为输出必须互为补码。这称为触发器的禁止或无效状态。

使用 NAND 门的异步 SR 触发器的真值表

基于此讨论,我们可以推导出使用 NAND 门实现的异步 SR 触发器的真值表。

| S | S' | R | R' | Q | 描述 |

|---|---|---|---|---|---|

| 0 | 1 | 0 | 1 | NC | 无变化 |

| 0 | 1 | 1 | 0 | 0 | 复位 |

| 1 | 0 | 0 | 1 | 1 | 置位 |

| 1 | 0 | 1 | 0 | X | 禁止 |

这就是数字电子学中异步或无时钟 SR 触发器的全部内容。